## SIEMENS

| Aicro<br>To PLC<br>57-200<br>ramming |

|--------------------------------------|

| 67-200                               |

|                                      |

| ramming                              |

|                                      |

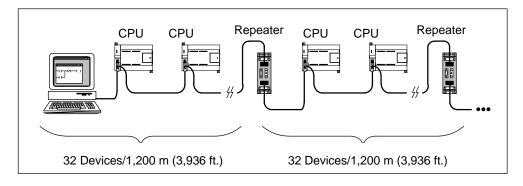

| es and                               |

|                                      |

| ons                                  |

|                                      |

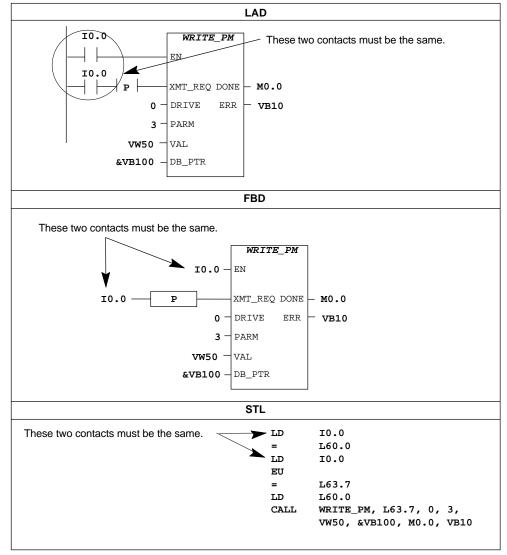

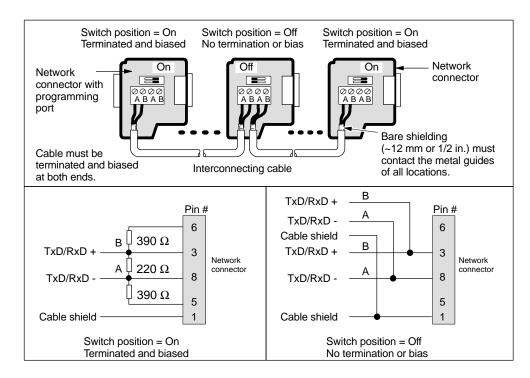

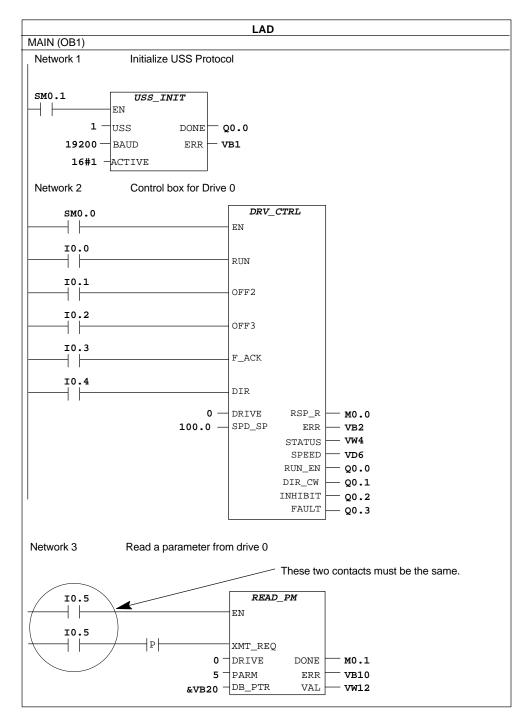

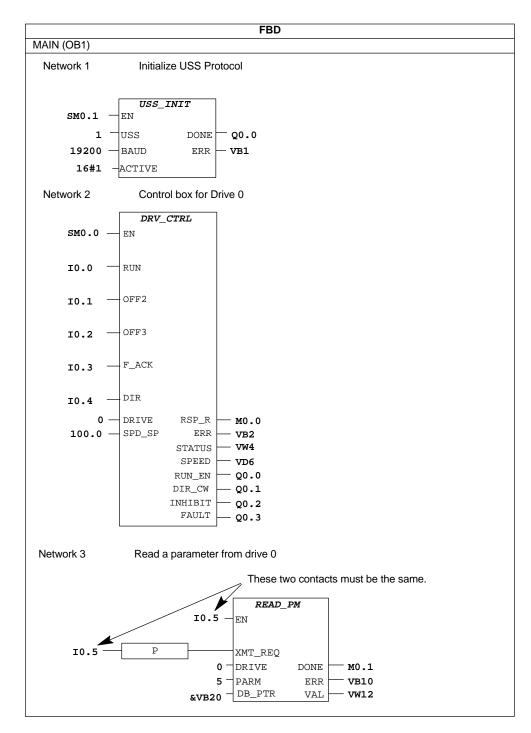

|                                      |

|                                      |

| ructions<br>ves                      |

|                                      |

|                                      |

|                                      |

| ts                                   |

| Guide                                |

|                                      |

|                                      |

|                                      |

|                                      |

Index

#### Notes on Safety

This manual contains notices which you should observe to ensure your own personal safety, as well as to protect the product and connected equipment. These notices are highlighted in the manual by a warning triangle and are marked as follows according to the level of danger:

#### Danger

indicates that death, severe personal injury or substantial property damage **will** result if proper precautions are not taken.

#### Warning

indicates that death, severe personal injury or substantial property damage **can** result if proper precautions are not taken.

#### Caution

indicates that minor personal injury or property damage can result if proper precautions are not taken.

#### Note

draws your attention to particularly important information on the product, handling the product, or to a particular part of the documentation.

Qualified Personnel Only qualified personnel should be allowed to install and work on this equipment. Qualified persons are defined as persons who are authorized to commission, to ground, and to tag circuits, equipment, and systems in accordance with established safety practices and standards.

Correct Usage

#### Note the following:

#### Warning

This device and its components may only be used for the applications described in the catalog or the technical description, and only in connection with devices or components from other manufacturers which have been approved or recommended by Siemens.

This product can only function correctly and safely if it is transported, stored, set up, and installed correctly, and operated and maintained as recommended.

Trademarks

SIMATIC®, SIMATIC NET® and SIMATIC NET® are registered trademarks of SIEMENS AG.

Third parties using for their own purposes any other names in this document which refer to trademarks might infringe upon the rights of the trademark owners.

#### Copyright ©Siemens AG 2000 All rights reserved

#### **Disclaimer of Liability**

The reproduction, transmission or use of this document or its contents is not permitted without express written authority. Offenders will be liable for damages. All rights, including rights created by patent grant or registration of a utility model or design, are reserved.

#### Siemens AG Bereich Automatisierungs- und Antriebstechnik Geschaeftsgebiet Industrie-Automatisierungssysteme Postfach 4848, D-90327 Nuernberg

We have checked the contents of this manual for agreement with the hardware and software described. Since deviations cannot be precluded entirely, we cannot guarantee full agreement. However, the data in this manual are reviewed regularly and any necessary corrections included in subsequent editions. Suggestions for improvement are welcomed.

© Siemens AG 2000 Subject to technical change.

Excellence in Automation & Drives: Siemens

Siemens Aktiengesellschaft

6ES7298-8FA21-8BH0

### Preface

#### Purpose

The S7-200 series is a line of micro-programmable logic controllers (Micro PLCs) that can control a variety of automation applications. Compact design, low cost, and a powerful instruction set make the S7-200 controllers a perfect solution for controlling small applications. The wide variety of CPU sizes and voltages and the Windows-based programming tool give you the flexibility you need to solve your automation problems.

The S7-200 product line has been redesigned to be smaller, faster, and to have increased functionality. The new S7-200 products are intended to replace the previous products.

This manual provides information about installing and programming the S7-200 Micro PLCs. The *S7-200 Programmable Controller System Manual* includes the following topics:

- Installing and wiring

- Understanding the CPU operations, data types and addressing modes, scan cycle, password protection, and network communication

- Specifications

- Descriptions and examples for the SIMATIC and IEC 11313 programming instructions

- Using the USS Protocol Instructions to communicate with drives

- Typical execution times for SIMATIC STL instructions

#### Audience

This manual is designed for engineers, programmers, installers, and electricians who have a general knowledge of programmable logic controllers.

#### Scope of the Manual

The information contained in this manual pertains in particular to the following products:

- S7-200 CPU models: CPU 221, CPU 222, and CPU 224 (firmware release 1.1), and CPU 226 (firmware release 1.0).

- STEP 7Micro/WIN 32, version 3.1, a 32-bit programming software package for Windows 95, Windows 98, and the Windows NT environment

- STEP 7Micro/WIN 32 Toolbox, a 32-bit programming software package for the Windows 95, Windows 98, and the Windows NT 4.0 environment.

STEP 7Micro/WIN 32 Toolbox is designed for customers who use the S7-200 CPU with other microsystem components (such as the TP070 Touch Panel or a MicroMaster drive).

#### **Agency Approvals**

The SIMATIC S7-200 series meets the following regulations:

- European Community (CE) Low Voltage Directive 73/23/EEC

- European Community (CE) EMC Directive 89/336/EEC

- Underwriters Laboratories, Inc.: UL 508 Listed (Industrial Control Equipment)

- Canadian Standards Association: CSA C22.2 Number 142 Certified (Process Control Equipment)

- Factory Mutual Research: FM Class I, Division 2, Groups A, B, C, & D Hazardous Locations, T4A and Class I, Zone 2, IIC, T4.

Refer to Appendix A for compliance information.

#### **Related Information**

Refer to the following for more detailed information about selected topics:

- STEP 7Micro/WIN 32 CD/disk: provides online help, the *STEP 7Micro/WIN Getting Started* (a printable online manual), and Tips and Tricks projects.

- STEP 7Micro/WIN 32 Toolbox CD: provides the TP070 Touch Panel Configuration Software, USS Protocol Instructions, online help, the *STEP 7Micro/WIN Getting Started* (a printable online manual), and Tips and Tricks projects.

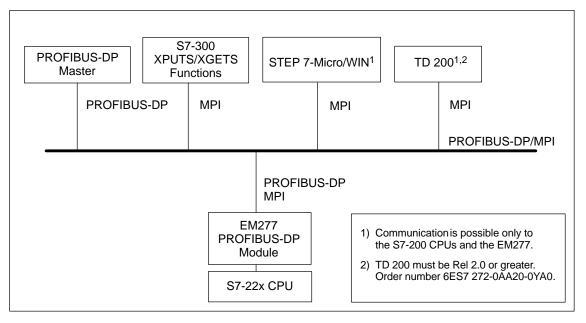

- Process Field Bus (PROFIBUS) standard (EN 50170): describes the standard protocol for the S7-200 DP communication capability.

- *TD 200 Operator Interface User Manual:* describes how to install and use the TD 200 with an S7-200 programmable logic controller.

#### How to Use This Manual

If you are a first-time (novice) user of S7-200 Micro PLCs, you should read the entire *S7-200 Programmable Controller System Manual*. If you are an experienced user, refer to the manual table of contents or index to find specific information.

The *S7-200 Programmable Controller System Manual* is organized according to the following topics:

- "Introducing the S7-200 Micro PLC" (Chapter 1) provides an overview of some of the features of the equipment.

- "Installing an S7-200 Micro PLC" (Chapter 2) provides procedures, dimensions, and basic guidelines for installing the S7-200 CPU modules and expansion I/O modules.

- "Getting Started with an S7-200 Programming System" (Chapter 3) describes how to set up an S7-200 programming system.

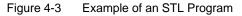

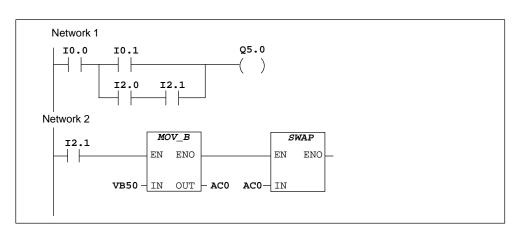

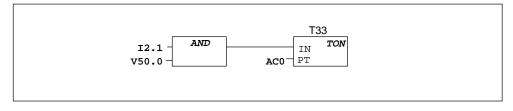

- "Basic Concepts for Programming an S7-200 CPU" (Chapter 4), "CPU Memory: Data Types and Addressing Modes" (Chapter 5), and "CPU and Input/Output Control" (Chapter 6) provide information about how the S7-200 CPU processes data and executes your program.

- "Setting Up Communications Hardware and Network Communications" (Chapter 7) provides information about how to install and remove communications hardware and how to connect the S7-200 CPU to different types of networks.

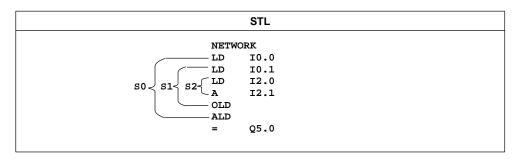

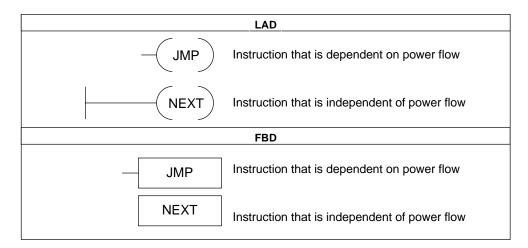

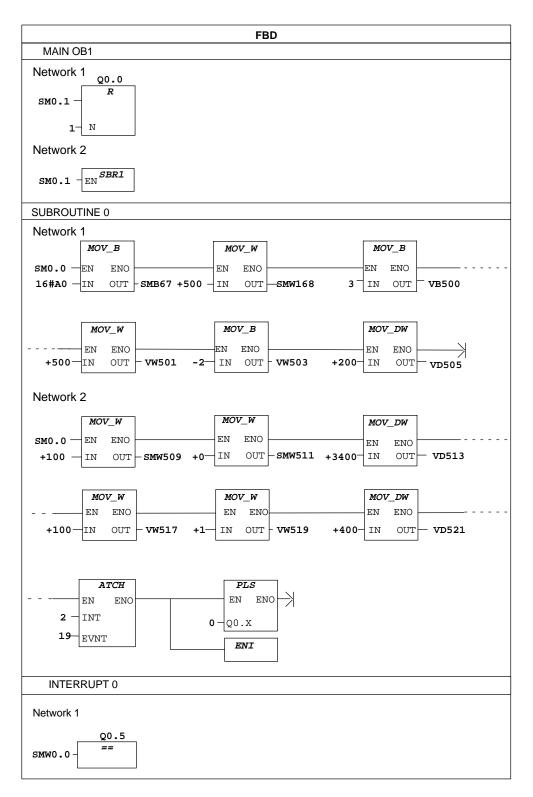

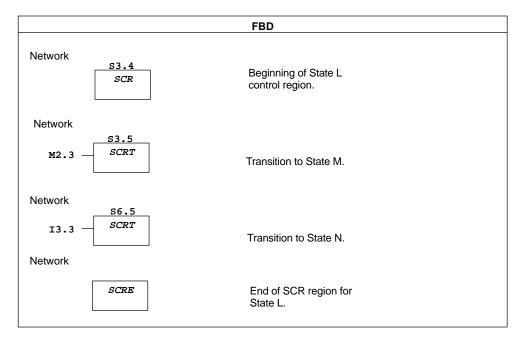

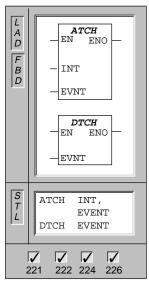

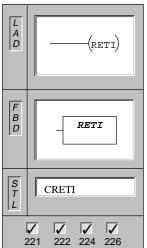

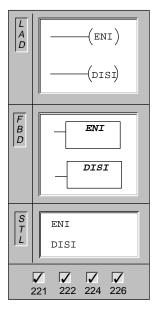

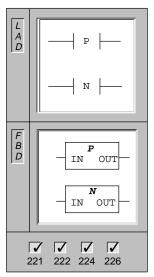

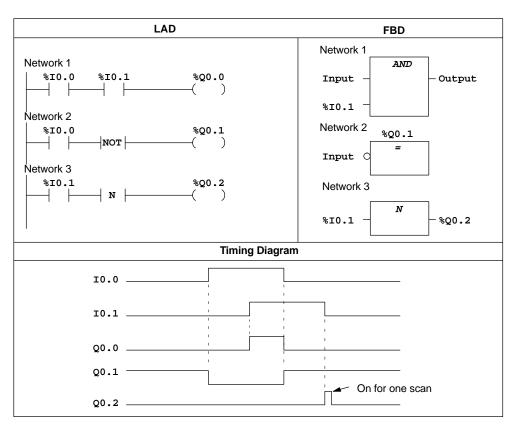

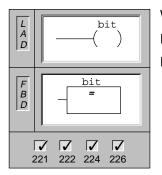

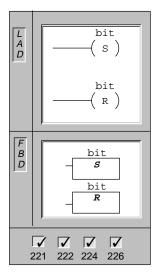

- "Conventions for S7-200 Instructions" (Chapter 8) provides an overview of the different programming language concepts and terminology.

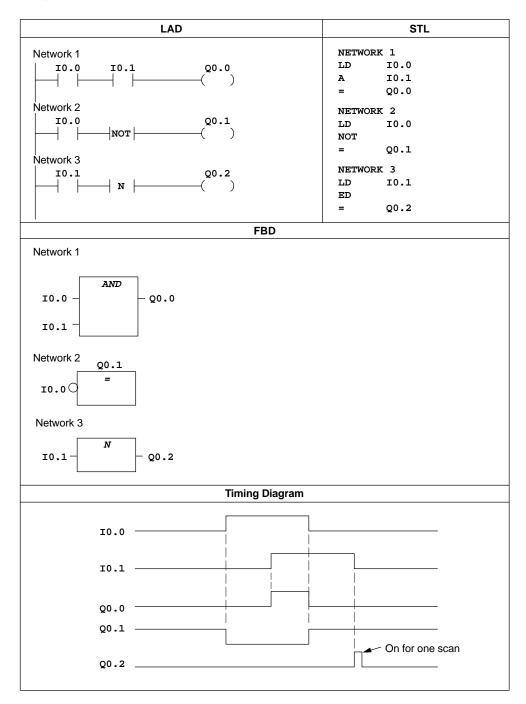

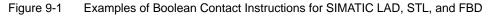

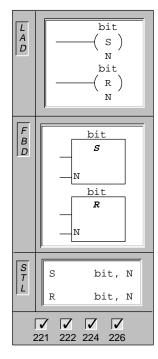

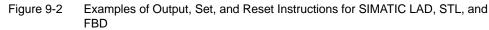

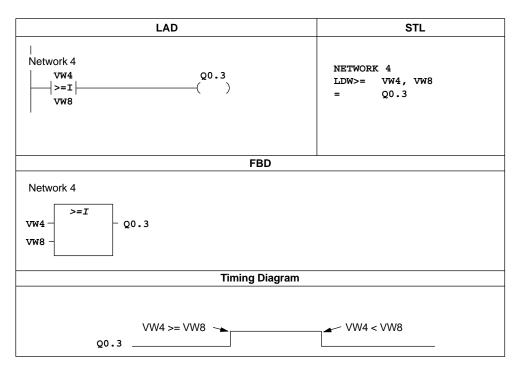

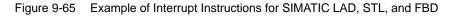

- "SIMATIC Instructions" (Chapter 9) provides descriptions and examples of SIMATIC LAD, FBD, and STL programming instructions.

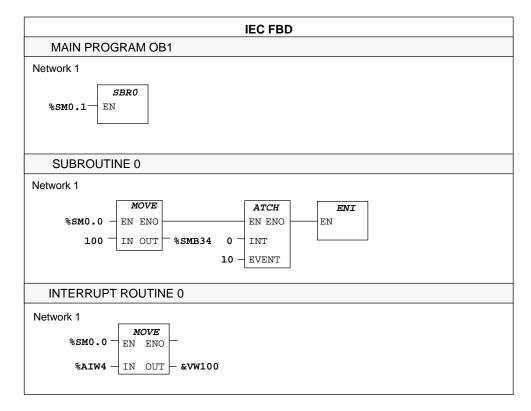

- "IEC 11313 Instructions" (Chapter 10) provides descriptions and examples of IEC 11313 LAD and FBD programming instructions.

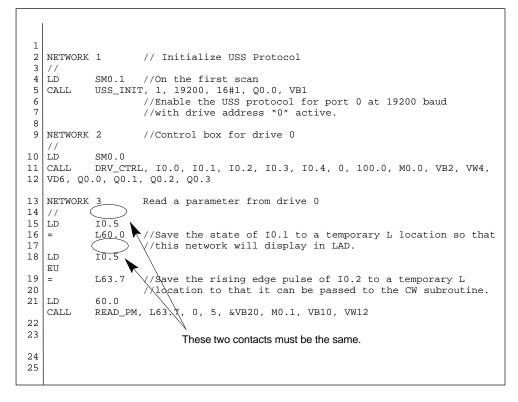

- "Using USS Protocol Instructions to Communicate with Drives" (Chapter 11) provides descriptions and examples of USS Protocol Instructions and information about how to use these instructions to communicate with drives.

Additional information (such as the equipment specifications, error code descriptions, troubleshooting, and STL instruction execution times) are provided in the appendices.

#### **Additional Assistance**

For assistance in answering technical questions, for training on this product, or for ordering, contact your Siemens distributor or sales office.

For Internet information about Siemens products and services, technical support, or FAQs (frequently asked questions) and application tips, use the following Internet addresses:

http://www.ad.siemens.de http://www.siemens.com/s7200 for general Siemens information for S7-200 product information

## Contents

| 1 | Introdu   | cing the S7-200 Micro PLC                                                 | 1-1  |

|---|-----------|---------------------------------------------------------------------------|------|

|   | 1.1       | Comparing the Features of the S7-200 Micro PLCs                           | 1-2  |

|   | 1.2       | Major Components of the S7-200 Micro PLC                                  | 1-5  |

|   | 1.3       | Maximum I/O Configurations                                                | 1-7  |

| 2 | Installir | ng an S7-200 PLC                                                          | 2-1  |

|   | 2.1       | Panel Layout Considerations                                               | 2-2  |

|   | 2.2       | Installing and Removing an S7-200 Micro PLC or Expansion Module           | 2-6  |

|   | 2.3       | Installing the Field Wiring                                               | 2-9  |

|   | 2.4       | Using Suppression Circuits                                                | 2-16 |

|   | 2.5       | Power Considerations                                                      | 2-18 |

| 3 | Getting   | Started with an S7-200 Programming System                                 | 3-1  |

|   | 3.1       | Overview                                                                  | 3-2  |

|   | 3.2       | Quick Start for STEP 7-Micro/WIN 32                                       | 3-3  |

|   | 3.3       | How Do I Set Up Communications Using the PC/PPI Cable?                    | 3-5  |

|   | 3.4       | How Do I Complete the Communications Connection?                          | 3-9  |

|   | 3.5       | How Do I Change the Communications Parameters for My PLC?                 | 3-10 |

| 4 | Basic C   | Concepts for Programming an S7-200 CPU                                    | 4-1  |

|   | 4.1       | Guidelines for Designing a Micro PLC System                               | 4-2  |

|   | 4.2       | Concepts of an S7-200 Program                                             | 4-5  |

|   | 4.3       | Concepts of the S7-200 Programming Languages and Editors                  | 4-6  |

|   | 4.4       | Understanding the Differences between SIMATIC and IEC 1131-3 Instructions | 4-10 |

|   | 4.5       | Basic Elements for Constructing a Program                                 | 4-18 |

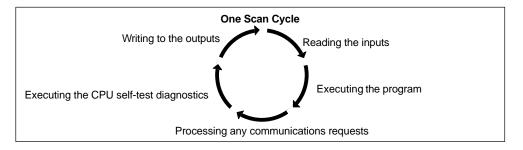

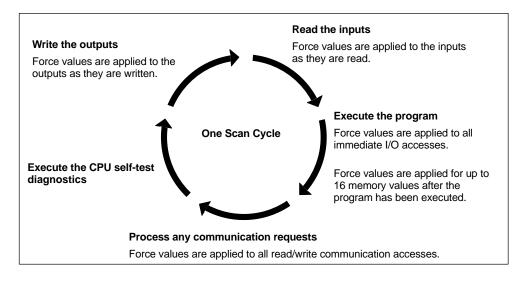

|   | 4.6       | Understanding the Scan Cycle of the CPU                                   | 4-22 |

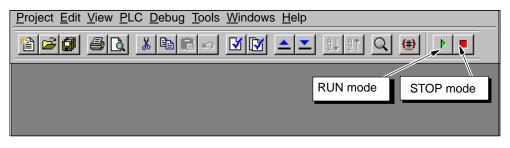

|   | 4.7       | Selecting the Mode of Operation for the CPU                               | 4-25 |

|   | 4.8       | Creating a Password for the CPU                                           | 4-27 |

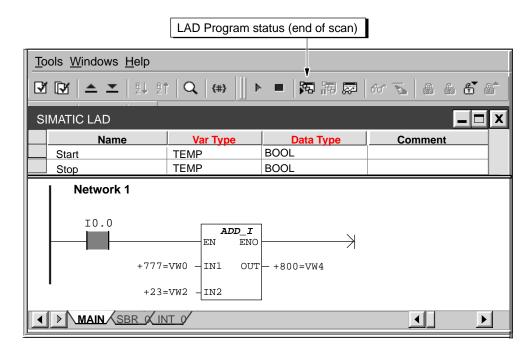

|   | 4.9       | Debugging and Monitoring Your Program                                     | 4-30 |

|   | 4.10      | Editing in RUN Mode                                                       | 4-39 |

|   | 4.11      | Background Time                                                           | 4-42 |

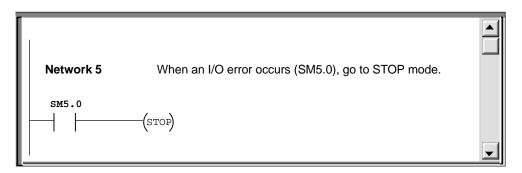

|   | 4.12      | Error Handling for the S7-200 CPU                                         | 4-43 |

|   |           |                                                                           |      |

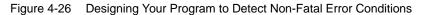

| 5 | CPU Me  | emory: Data Types and Addressing Modes                        | 5-1  |

|---|---------|---------------------------------------------------------------|------|

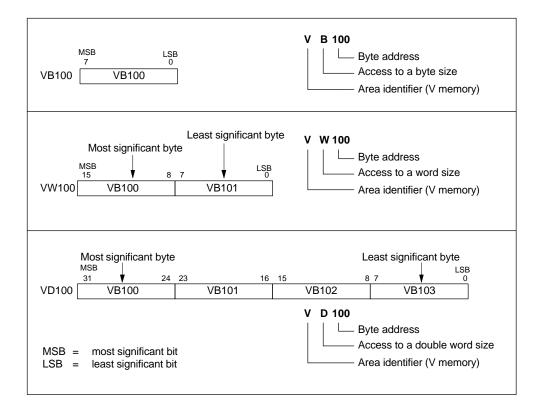

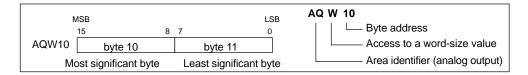

|   | 5.1     | Direct Addressing of the CPU Memory Areas                     | 5-2  |

|   | 5.2     | SIMATIC Indirect Addressing of the CPU Memory Areas           | 5-13 |

|   | 5.3     | Memory Retention for the S7-200 CPU                           | 5-15 |

|   | 5.4     | Using Your Program to Store Data Permanently                  | 5-20 |

|   | 5.5     | Using a Memory Cartridge to Store Your Program                | 5-22 |

| 6 | CPU an  | d Input/Output Configuration                                  | 6-1  |

|   | 6.1     | Local I/O and Expansion I/O                                   | 6-2  |

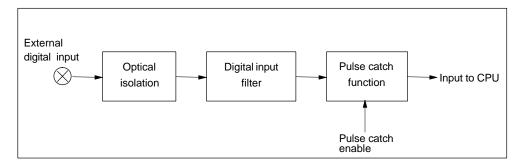

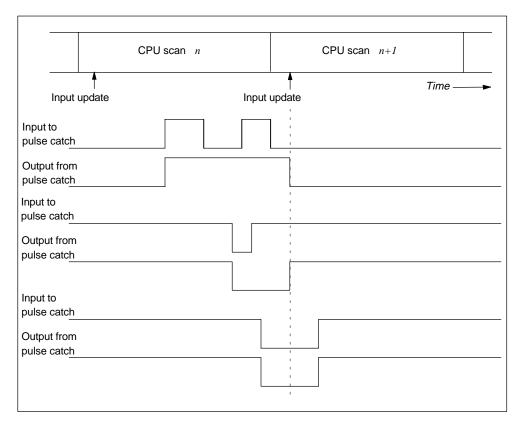

|   | 6.2     | Using the Selectable Input Filter to Provide Noise Rejection  | 6-4  |

|   | 6.3     | Pulse Catch                                                   | 6-5  |

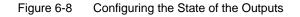

|   | 6.4     | Using the Output Table to Configure the States of the Outputs | 6-8  |

|   | 6.5     | Analog Input Filter                                           | 6-9  |

|   | 6.6     | High-Speed I/O                                                | 6-10 |

|   | 6.7     | Analog Adjustments                                            | 6-13 |

| 7 | Setting | Up Communications Hardware and Network Communications         | 7-1  |

|   | 7.1     | What Are My Communication Choices?                            | 7-2  |

|   | 7.2     | Installing and Removing Communication Interfaces              | 7-7  |

|   | 7.3     | Selecting and Changing Parameters                             | 7-9  |

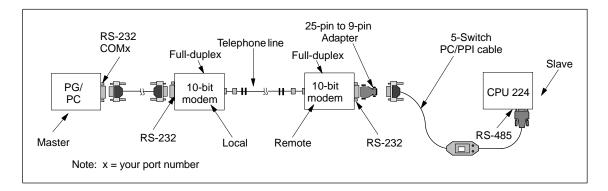

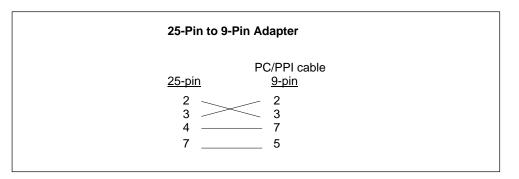

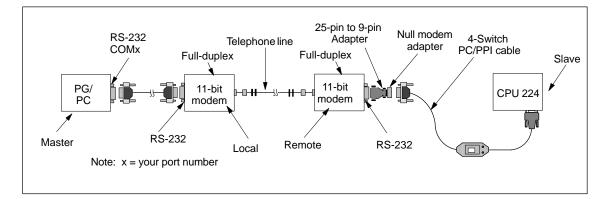

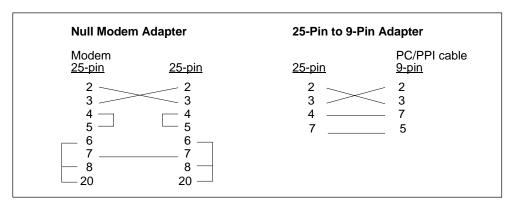

|   | 7.4     | Communicating With Modems                                     | 7-16 |

|   | 7.5     | Network Overview                                              | 7-27 |

|   | 7.6     | Network Components                                            | 7-32 |

|   | 7.7     | Using the PC/PPI Cable with Other Devices and Freeport        | 7-36 |

|   | 7.8     | Network Performance                                           | 7-42 |

| 8 | Conven  | tions for S7-200 Instructions                                 | 8-1  |

|   | 8.1     | Concepts and Conventions For STEP 7-Micro/WIN 32 Programming  | 8-2  |

|   | 8.2     | Valid Ranges for the S7-200 CPUs                              | 8-7  |

| 9 | SIMATIO | C Instructions                                                | 9-1  |

|   | 9.1     | SIMATIC Bit Logic Instructions                                | 9-2  |

|   | 9.2     | SIMATIC Compare Instructions                                  | 9-10 |

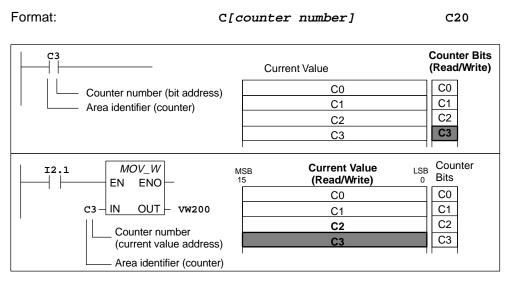

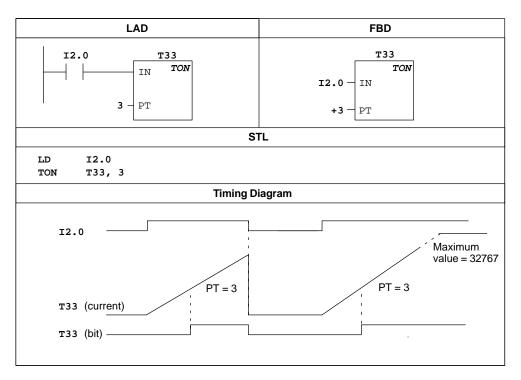

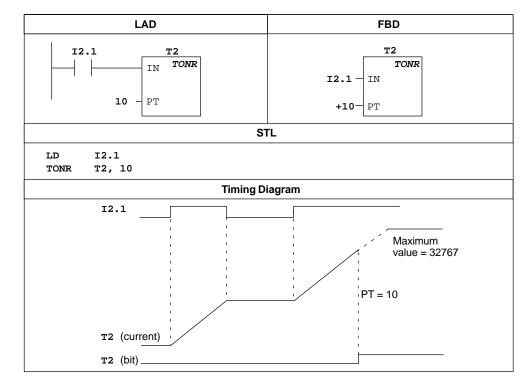

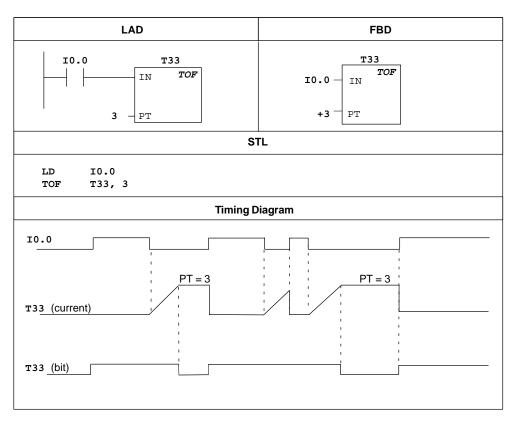

|   | 9.3     | SIMATIC Timer Instructions                                    | 9-15 |

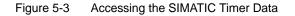

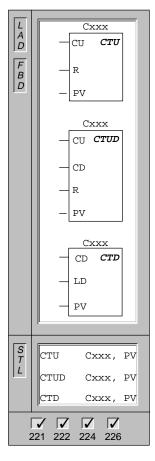

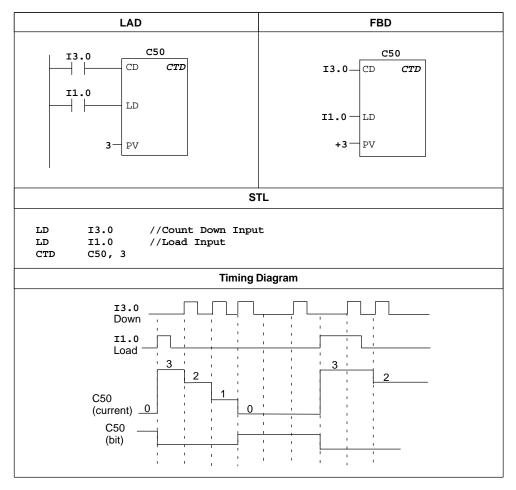

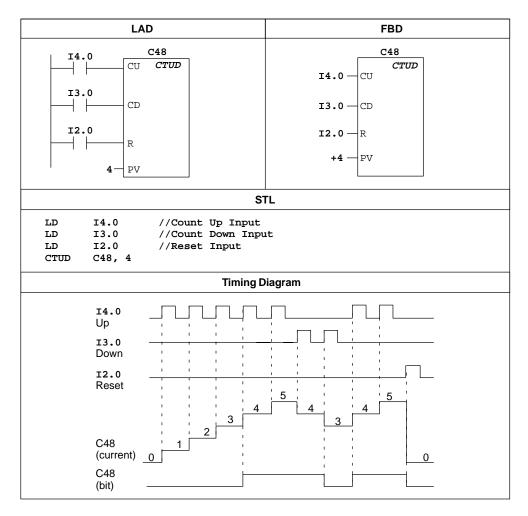

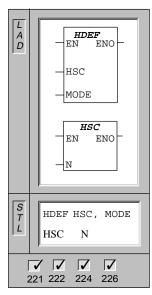

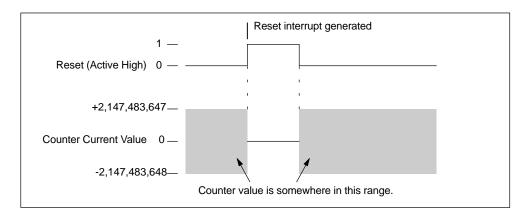

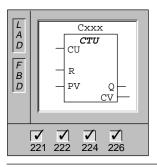

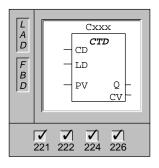

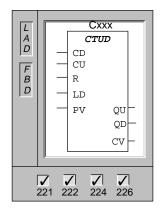

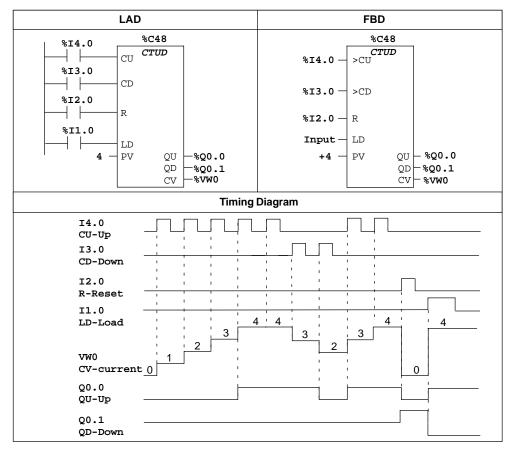

|   | 9.4     | SIMATIC Counter Instructions                                  | 9-23 |

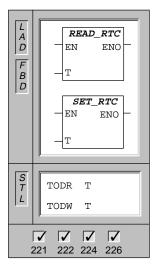

|   | 9.5     | SIMATIC Clock Instructions                                    | 9-71 |

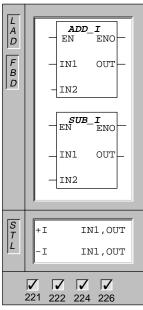

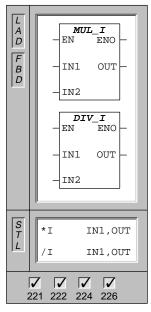

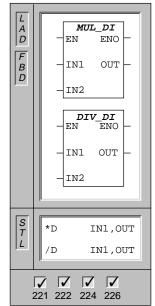

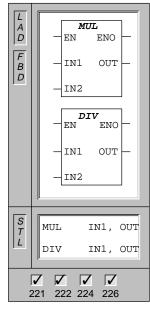

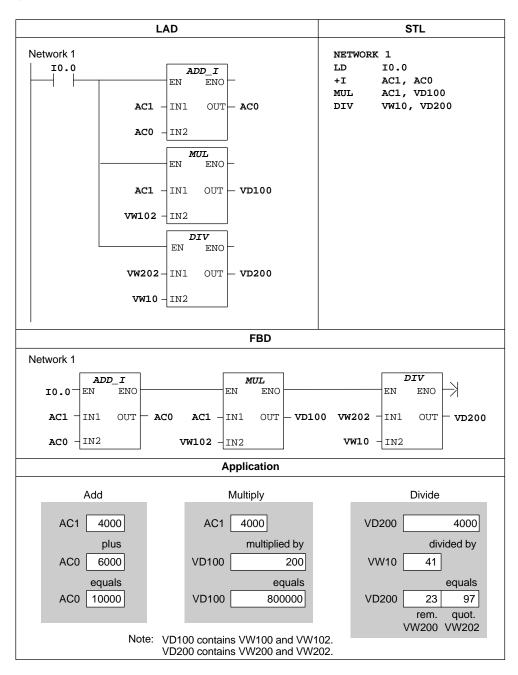

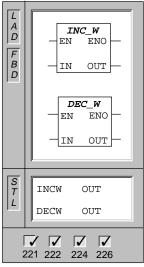

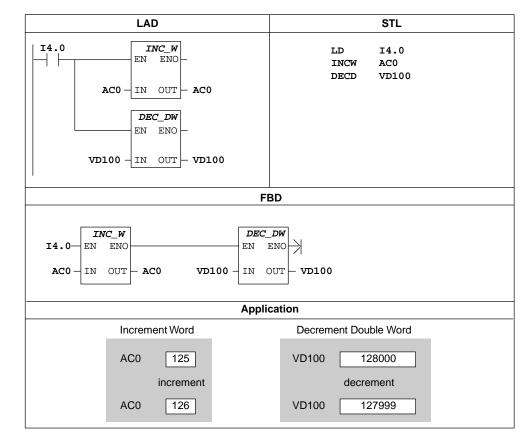

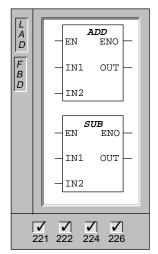

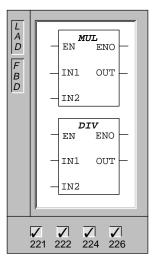

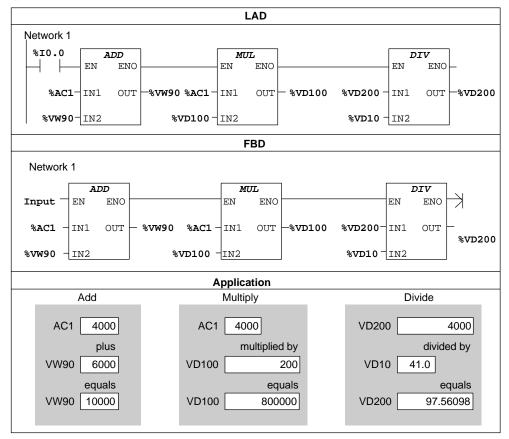

|   | 9.6     | SIMATIC Integer Math Instructions                             | 9-73 |

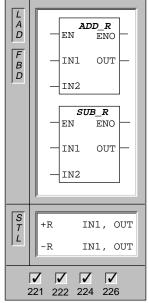

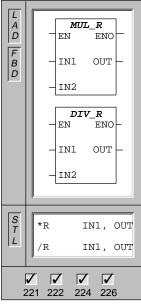

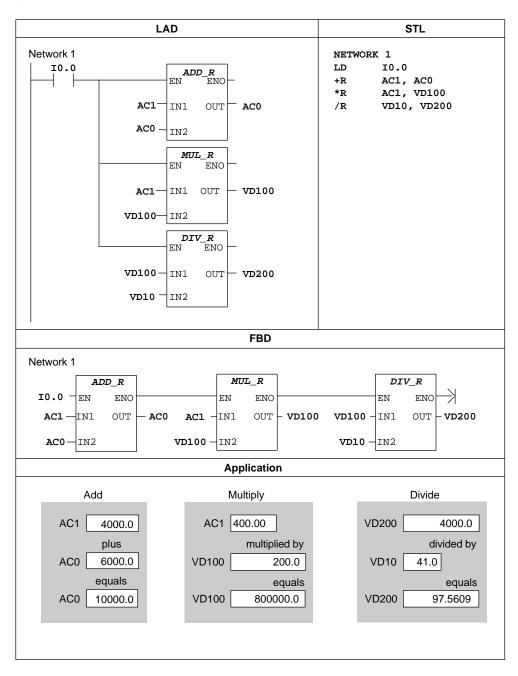

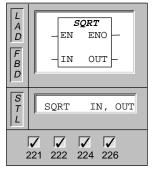

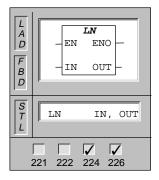

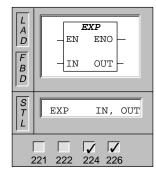

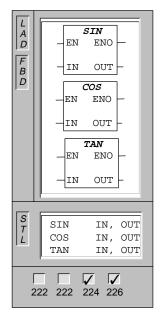

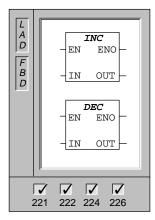

|   | 9.7     | SIMATIC Real Math Instructions                                | 9-82 |

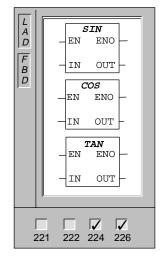

|   | 9.8     | SIMATIC Numerical Functions Instructions                      | 9-85 |

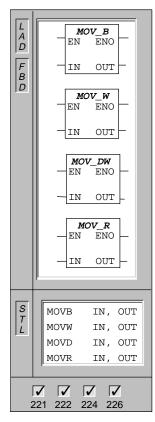

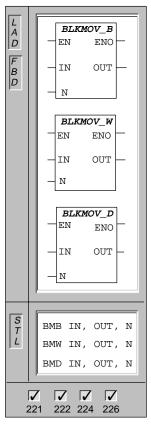

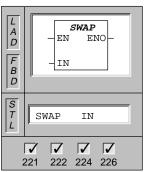

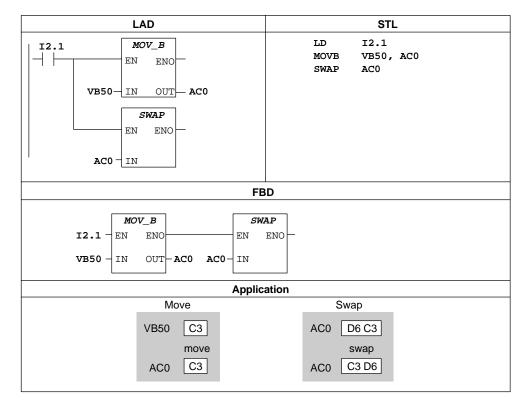

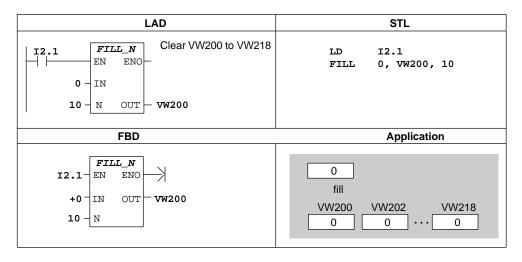

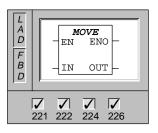

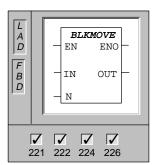

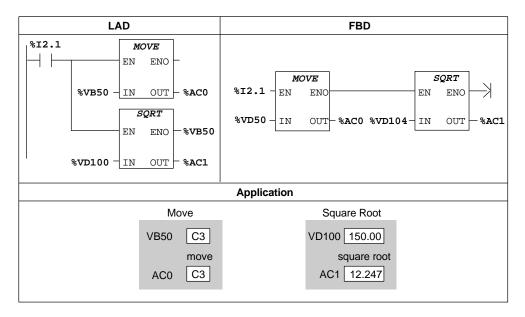

|    | 9.9      | SIMATIC Move Instructions                           | 9-102 |

|----|----------|-----------------------------------------------------|-------|

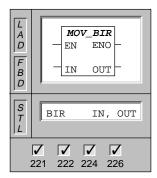

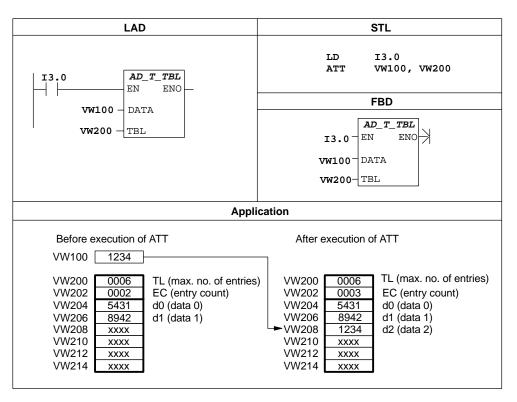

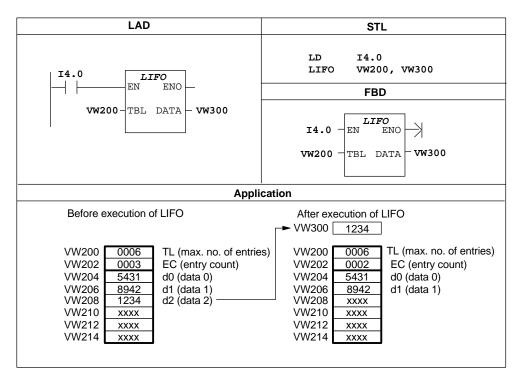

|    | 9.10     | SIMATIC Table Instructions                          | 9-107 |

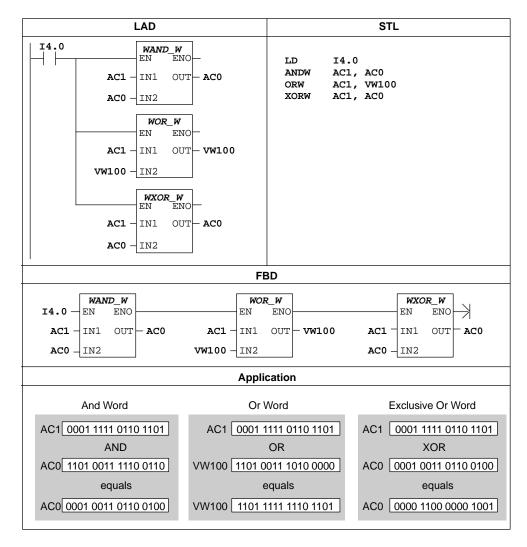

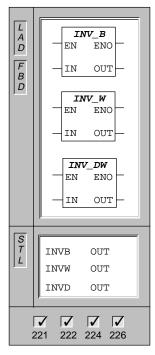

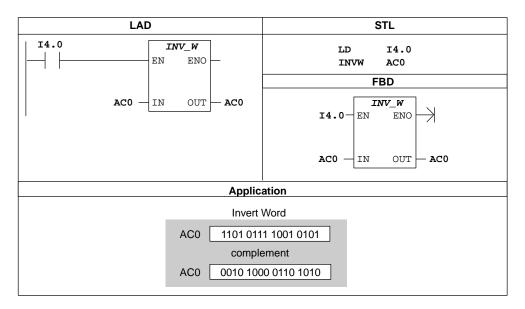

|    | 9.11     | SIMATIC Logical Operations Instructions             | 9-114 |

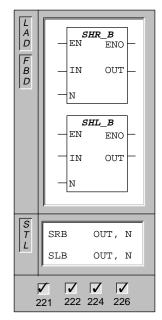

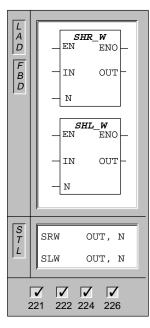

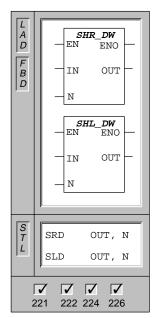

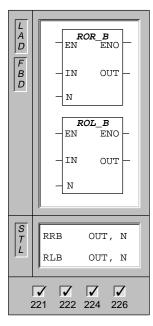

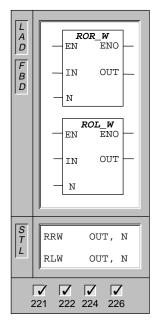

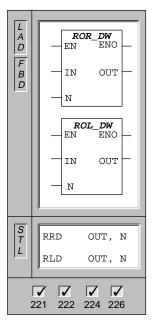

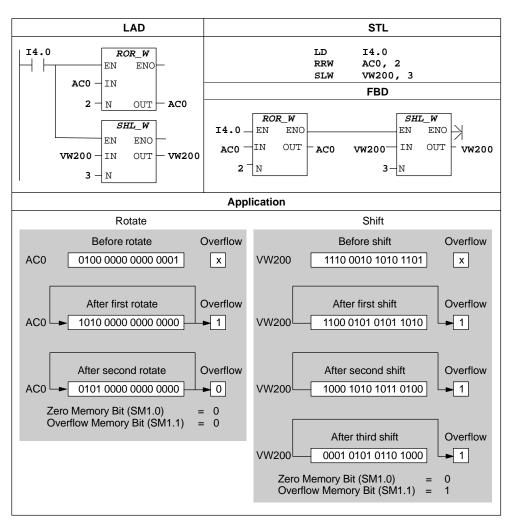

|    | 9.12     | SIMATIC Shift and Rotate Instructions               | 9-120 |

|    | 9.13     | SIMATIC Conversion Instructions                     | 9-130 |

|    | 9.14     | SIMATIC Program Control Instructions                | 9-145 |

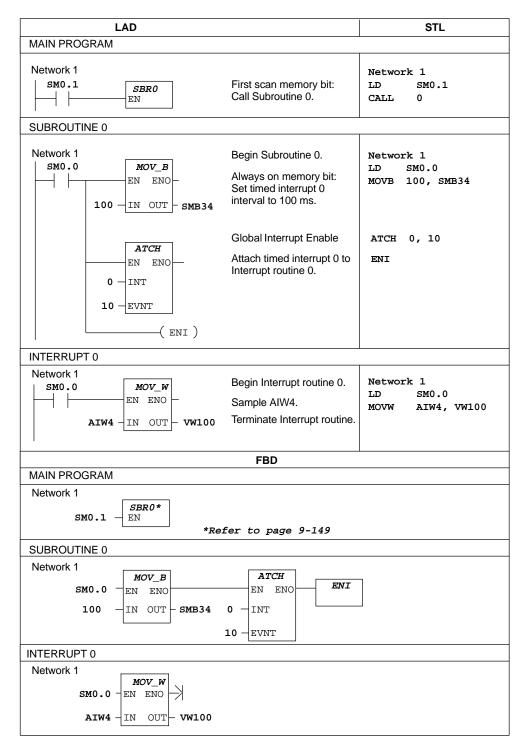

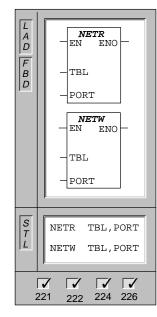

|    | 9.15     | SIMATIC Interrupt and Communications Instructions   | 9-169 |

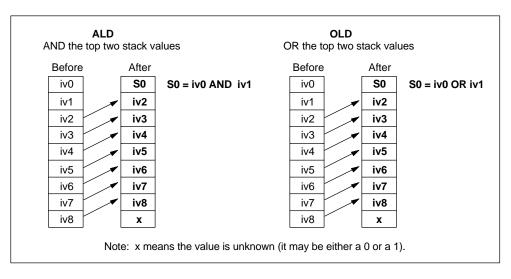

|    | 9.16     | SIMATIC Logic Stack Instructions                    | 9-197 |

| 10 | IEC 1131 | 1-3 Instructions                                    | 10-1  |

|    | 10.1     | IEC Bit Logic Instructions                          | 10-2  |

|    | 10.2     | IEC Compare Instructions                            | 10-8  |

|    | 10.3     | IEC Timer Instructions                              | 10-11 |

|    | 10.4     | IEC Counter Instructions                            | 10-15 |

|    | 10.5     | IEC Math Instructions                               | 10-18 |

|    | 10.6     | IEC Numerical Functions Instructions                | 10-21 |

|    | 10.7     | IEC Move Instructions                               | 10-23 |

|    | 10.8     | IEC Logic Instructions                              | 10-25 |

|    | 10.9     | IEC Shift and Rotate Instructions                   | 10-27 |

|    | 10.10    | IEC Conversion Instructions                         | 10-30 |

| 11 | Using U  | SS Protocol Instructions to Communicate with Drives | 11-1  |

|    | 11.1     | USS Protocol Instruction Requirements               | 11-2  |

|    | 11.2     | Programming Sequence                                | 11-4  |

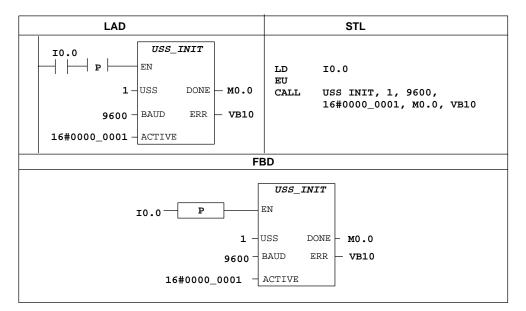

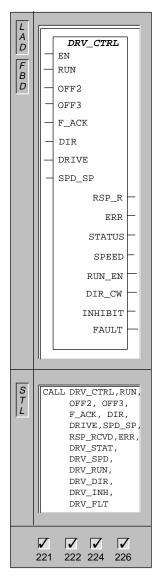

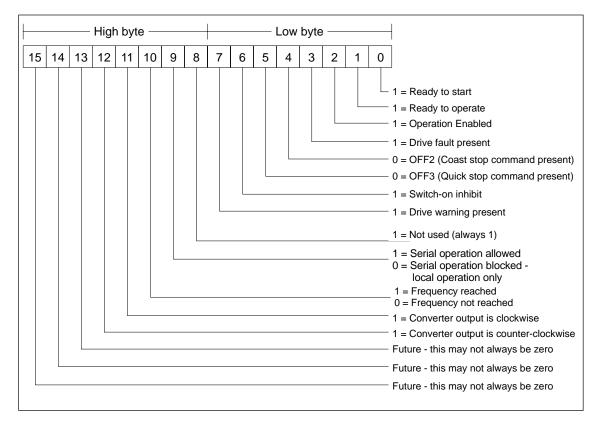

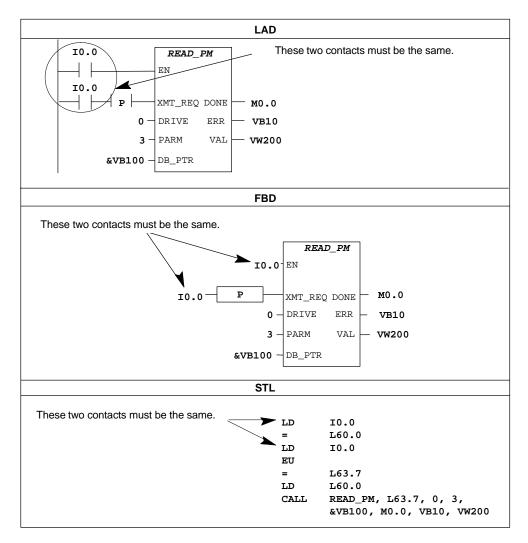

|    | 11.3     | USS Protocol Instructions                           | 11-5  |

|    | 11.4     | Connecting the Drives                               | 11-17 |

|    | 11.5     | Drive Setup                                         | 11-18 |

| Α | S7-200 \$                            | Specifications                                                                                  | A-1   |  |  |

|---|--------------------------------------|-------------------------------------------------------------------------------------------------|-------|--|--|

|   | A.1                                  | General Technical Specifications                                                                | A-2   |  |  |

|   | A.2                                  | Specifications for the CPU 221, Firmware Release 1.1                                            | A-6   |  |  |

|   | A.3                                  | Specifications for the CPU 222, Firmware Release 1.1                                            | A-11  |  |  |

|   | A.4                                  | Specifications for the CPU 224, Firmware Release 1.1                                            | A-16  |  |  |

|   | A.5                                  | Specifications for the CPU 226                                                                  | A-21  |  |  |

|   | A.6                                  | Specifications for the EM 221 Digital Input Module                                              | A-26  |  |  |

|   | A.7                                  | Specifications for the EM 222 Digital Output Modules                                            | A-28  |  |  |

|   | A.8                                  | Specifications for the EM 223 Digital Combination Modules,<br>4 Inputs/4 Outputs                | A-30  |  |  |

|   | A.9                                  | Specifications for the EM 223 Digital Combination Modules,<br>8 Inputs/8 Outputs                | A-33  |  |  |

|   | A.10                                 | Specifications for the EM 223 Digital Combination Modules, 16 Inputs/16 Outputs                 | A-36  |  |  |

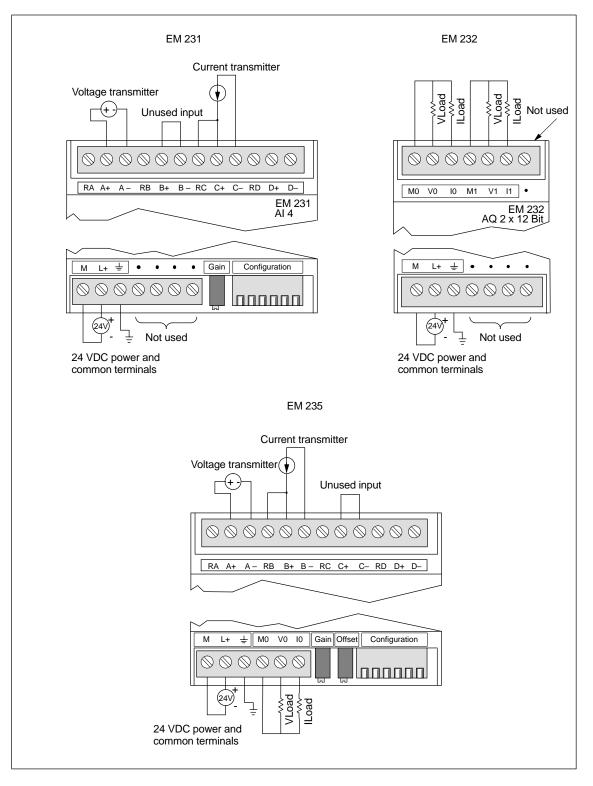

|   | A.11                                 | Specifications for the EM 231, EM 232, and EM 235 Analog Input, Output, and Combination Modules | A-39  |  |  |

|   | A.12                                 | Specifications for the EM 277 PROFIBUS-DP Module                                                | A-50  |  |  |

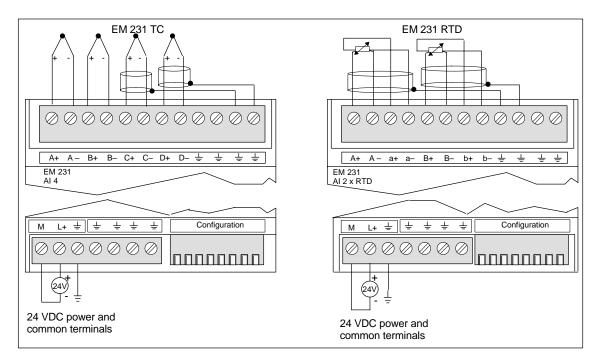

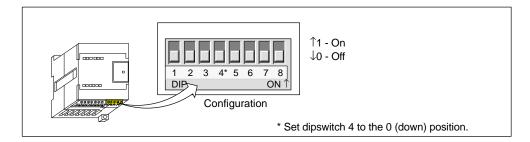

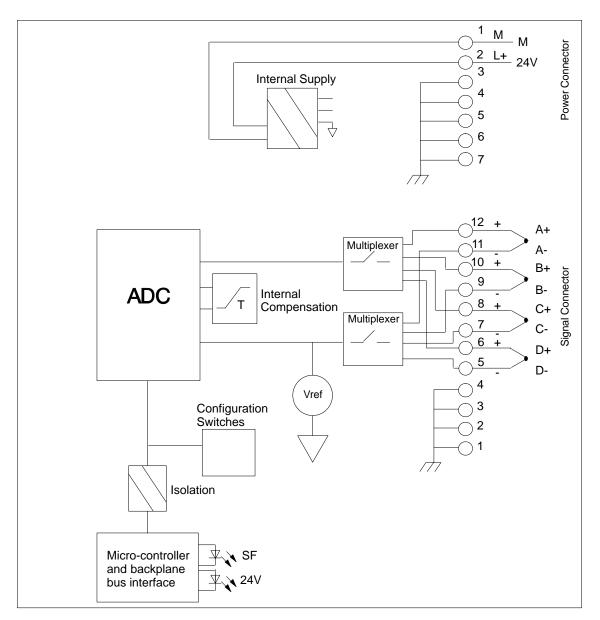

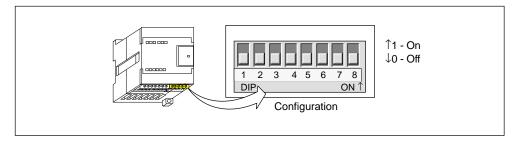

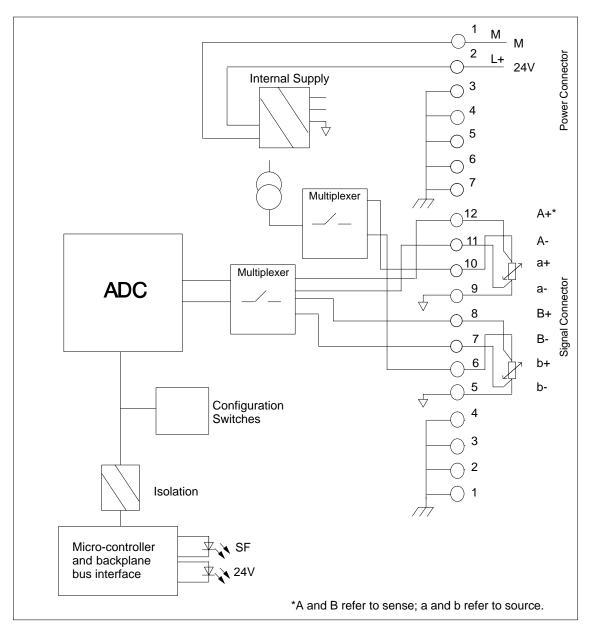

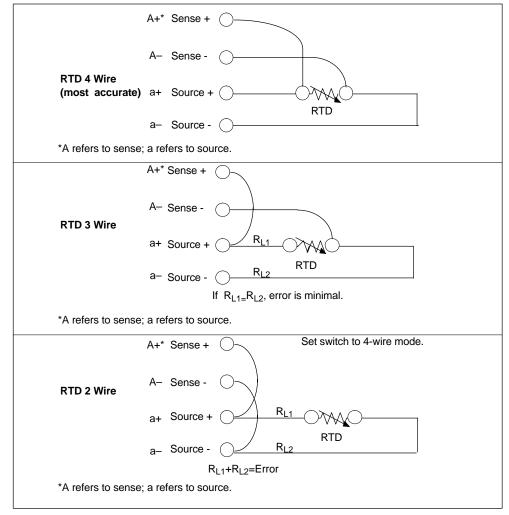

|   | A.13                                 | Specifications for EM 231 Thermocouple, EM 231 RTD Modules                                      | A-67  |  |  |

|   | A.14                                 | CP 243-2 Communications Processor                                                               | A-85  |  |  |

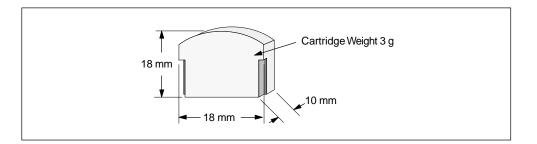

|   | A.15                                 | Optional Cartridges                                                                             | A-88  |  |  |

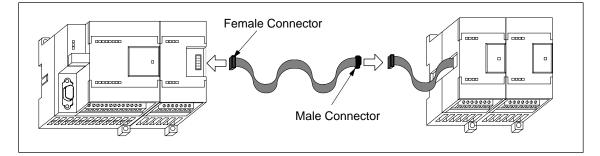

|   | A.16                                 | I/O Expansion Cable                                                                             | A-89  |  |  |

|   | A.17                                 | PC/PPI Cable                                                                                    | A-90  |  |  |

|   | A.18                                 | Input Simulators                                                                                | A-93  |  |  |

| в | Error Co                             | odes                                                                                            | B-1   |  |  |

|   | B.1                                  | Fatal Error Codes and Messages                                                                  | B-2   |  |  |

|   | B.2                                  | Run-Time Programming Problems                                                                   | B-3   |  |  |

|   | B.3                                  | Compile Rule Violations                                                                         | B-4   |  |  |

| С | Special                              | Memory (SM) Bits                                                                                | C-1   |  |  |

| D | S7-200 T                             | 200 Troubleshooting Guide                                                                       |       |  |  |

| Е | S7-200 Order Numbers E               |                                                                                                 |       |  |  |

| F | Executio                             | on Times for STL Instructions                                                                   | F-1   |  |  |

| G | S7-200 Quick Reference Information G |                                                                                                 |       |  |  |

|   | Index .                              | In                                                                                              | dex-1 |  |  |

# 1

## Introducing the S7-200 Micro PLC

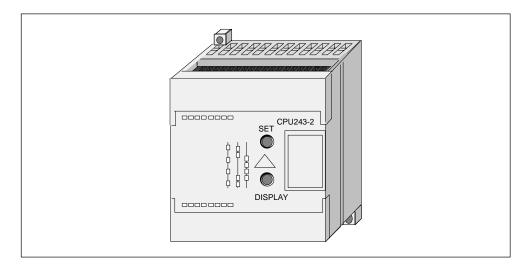

The S7-200 series is a line of micro-programmable logic controllers (Micro PLCs) that can control a variety of automation applications. Figure 1-1 shows an S7-200 Micro PLC. The compact design, expandability, low cost, and powerful instruction set of the S7-200 Micro PLC make a perfect solution for controlling small applications. In addition, the wide variety of CPU sizes and voltages provides you with the flexibility you need to solve your automation problems.

Figure 1-1 S7-200 Micro PLC

#### **Chapter Overview**

| Section | Description                                     | Page |

|---------|-------------------------------------------------|------|

| 1.1     | Comparing the Features of the S7-200 Micro PLCs | 1-2  |

| 1.2     | Major Components of the S7-200 Micro PLC        | 1-5  |

| 1.3     | Maximum I/O Configurations                      | 1-7  |

#### 1.1 Comparing the Features of the S7-200 Micro PLCs

#### **Equipment Requirements**

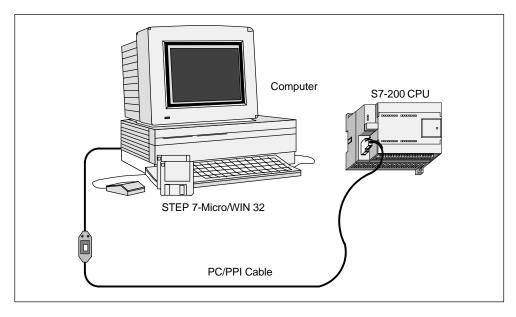

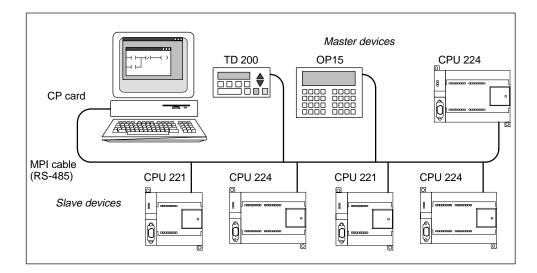

Figure 1-2 shows the basic S7-200 Micro PLC system, which includes an S7-200 CPU, a personal computer, STEP 7-Micro/WIN 32, version 3.1 programming software, and a communications cable.

In order to use a personal computer (PC), you must have one of the following:

- A PC/PPI cable

- A communications processor (CP) and multipoint interface (MPI) cable

- A multipoint interface (MPI) card. A communications cable is provided with the MPI card.

Figure 1-2 Components of an S7-200 Micro PLC System

#### Capabilities of the S7-200 CPUs

The S7-200 family includes a wide variety of CPUs. This variety provides a range of features to aid in designing a cost-effective automation solution. Table 1-1 provides a summary of the major features of the S7-200 CPUs, firmware release 1.1.

| Feature                                                                 | CPU 221                  | CPU 222                  | CPU 224                     | CPU 226                   |

|-------------------------------------------------------------------------|--------------------------|--------------------------|-----------------------------|---------------------------|

| Physical Size of Unit                                                   | 90 mm x 80 mm x<br>62 mm | 90 mm x 80 mm x<br>62 mm | 120.5 mm x<br>80 mm x 62 mm | 190 mm x<br>80 mm x 62 mm |

| Memory                                                                  | 1                        |                          |                             |                           |

| Program                                                                 | 2048 words               | 2048 words               | 4096 words                  | 4096 words                |

| User data                                                               | 1024 words               | 1024 words               | 2560 words                  | 2560 words                |

| User program storage                                                    | EEPROM                   | EEPROM                   | EEPROM                      | EEPROM                    |

| Data backup<br>(super capacitor)                                        | 50 hours typical         | 50 hours typical         | 190 hours typical           | 190 hours typical         |

| Local I/O                                                               |                          |                          |                             |                           |

| Local I/O                                                               | 6 In/4 Out               | 8 In/6 Out               | 14 In/10 Out                | 24 In/16 Out              |

| Number of expansion modules                                             | none                     | 2 modules                | 7 modules                   | 7 modules                 |

| Total I/O                                                               |                          |                          |                             |                           |

| Digital I/O image size                                                  | 256<br>(128 In/128 Out)  | 256<br>(128 In/128 Out)  | 256<br>(128 In/128 Out)     | 256<br>(128 In/128 Out)   |

| Analog I/O image size                                                   | none                     | 16 In/16 Out             | 32 In/32 Out                | 32 In/32 Out              |

| Actual I/O count that can be reali<br>the physical number of I/O points |                          |                          | e register size, module     | count, 5V power, and      |

| Instructions                                                            |                          |                          |                             |                           |

| Boolean execution speed at 33<br>MHz                                    | 0.37µs/<br>instruction   | 0.37 μs/<br>instruction  | 0.37 μs/<br>instruction     | 0.37 μs/<br>instruction   |

| I/O Image Register                                                      | 128 I and 128 Q          | 128 I and 128 Q          | 128 I and 128 Q             | 128 I and 128 Q           |

| Internal relays                                                         | 256                      | 256                      | 256                         | 256                       |

| Counters/Timers                                                         | 256/256                  | 256/256                  | 256/256                     | 256/256                   |

| Word In / Word Out                                                      | None                     | 16/16                    | 32/32                       | 32/32                     |

| Sequential control relays                                               | 256                      | 256                      | 256                         | 256                       |

| For/Next loops                                                          | Yes                      | Yes                      | Yes                         | Yes                       |

| Integer math (+ - * /)                                                  | Yes                      | Yes                      | Yes                         | Yes                       |

| Real math (+ - * /)                                                     | Yes                      | Yes                      | Yes                         | Yes                       |

| Enhanced Features                                                       |                          |                          |                             |                           |

| Built-in high-speed counter                                             | 4 H/W (20 KHz)           | 4 H/W (20 KHz)           | 6 H/W (20 KHz)              | 6 H/W (20 KHz)            |

| Analog adjustments                                                      | 1                        | 1                        | 2                           | 2                         |

| Pulse outputs                                                           | 2 (20 KHz,<br>DC only)   | 2 (20 KHz,<br>DC only)   | 2 (20 KHz,<br>DC only)      | 2 (20 KHz,<br>DC only)    |

| Communication interrupts                                                | 1 transmit/<br>2 receive | 1 transmit/<br>2 receive | 1 transmit/<br>2 receive    | 2 transmit/<br>4 receive  |

| Timed interrupts                                                        | 2<br>(1 ms to 255 ms)    | 2<br>(1 ms to 255 ms)    | 2<br>(1 ms to 255 ms)       | 2<br>(1 ms to 255 ms)     |

| Hardware input interrupts                                               | 4, input filter          | 4, input filter          | 4, input filter             | 4, input filter           |

| Real-time clock                                                         | Yes (cartridge)          | Yes (cartridge)          | Yes (built-in)              | Yes (built-in)            |

| Password protection                                                     | Yes                      | Yes                      | Yes                         | Yes                       |

Table 1-1Summary of the S7-200 CPU

| Table 1-1 | Summary of the S7-200 CPU |

|-----------|---------------------------|

|-----------|---------------------------|

| Communications        |                     |                     |                    |                     |

|-----------------------|---------------------|---------------------|--------------------|---------------------|

| Number of comm ports: | 1 (RS-485)          | 1 (RS-485)          | 1 (RS-485)         | 2 (RS-485)          |

| Protocols supported   |                     |                     |                    |                     |

| Port 0:               | PPI, DP/T, Freeport | PPI, DP/T, Freeport | PPI,DP/T, Freeport | PPI,DP/T, Freeport  |

| Port 1:               | N/A                 | N/A                 | N/A                | PPI, DP/T, Freeport |

| PROFIBUS peer-to-peer | (NETR/NETW)         | (NETR/NETW)         | (NETR/NETW)        | (NETR/NETW)         |

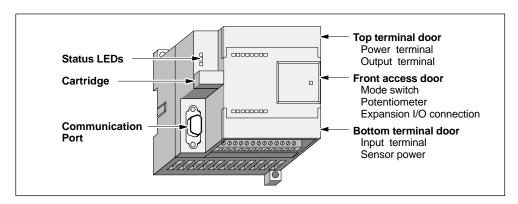

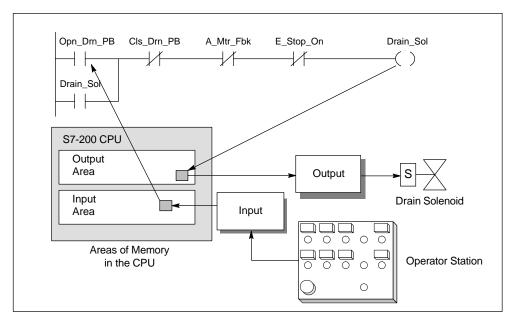

#### 1.2 Major Components of the S7-200 Micro PLC

An S7-200 Micro PLC consists of an S7-200 CPU alone or with a variety of optional expansion modules.

#### S7-200 CPU

The S7-200 CPU combines a central processing unit (CPU), power supply, and discrete I/O points into a compact, stand-alone device.

- The CPU executes the program and stores the data for controlling the automation task or process.

- The digital inputs and outputs are the system control points: the inputs monitor the signals from the field devices (such as sensors and switches), and the outputs control pumps, motors, or other devices in your process.

- The power supply provides electrical power for the CPU and for any expansion module that is connected.

- The communications port(s) allow you to connect the CPU to a programming device or to other devices.

- Status lights provide visual information about the CPU mode (RUN or STOP), the current state of the local I/O, and whether a system fault has been detected.

- Additional I/O points can be added to the CPU with expansion modules. (The CPU 221 is not expandable.)

- Higher performance communications can be added with expansion modules.

- Some CPUs provide a real-time clock as a built-in feature, while other CPUs have an optional real-time clock cartridge.

- An optional plug-in serial EEPROM cartridge provides a means to store CPU programs and transfer programs from one CPU to another.

- An optional plug-in battery cartridge provides extended retention of data memory in RAM.

Figure 1-3 shows the S7-200 CPU.

Figure 1-3 S7-200 CPU

#### **Expansion Modules**

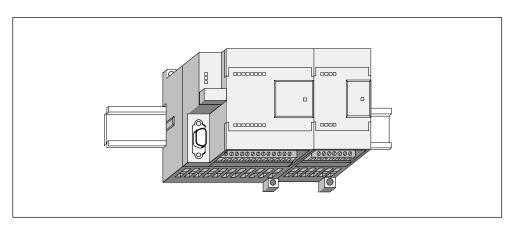

The S7-200 CPU provides a certain number of local I/O. Adding an expansion module provides additional input or output points (see Figure 1-4).

Figure 1-4 CPU with an Expansion Module

#### 1.3 Maximum I/O Configurations

The maximum I/O configuration for each CPU system is subject to the following limits:

Module count:

CPU 221: no expansion available

CPU 222: maximum of 2 expansion modules

CPU 224 and CPU 226: maximum of 7 expansion modules

No more than 2 of the 7 modules can be intelligent expansion modules (EM 277 PROFIBUS-DP modules)

- Digital Image Register size: The logical space that each CPU allows for digital I/O is 128 inputs and 128 outputs. Some physical points cannot be realized in this logical space because this space is allocated in blocks of 8 points. An 8-point block may not be completely realized by a specific module. For example, the CPU 224 with 10 actual outputs consumes 16 points of logical output space. A 4-input/4-output module consumes 8 inputs and 8 outputs of logical space. At the time of printing of this manual, there is no combination of current release CPU and I/O modules that causes this item to be a limit. It can be a limit in systems including prior release CPU 22x or future release products.

- Analog Image Register size: The logical space allowed for analog I/O is:

CPU 222: 16 inputs and 16 outputs

CPU 224 and CPU 226: 32 inputs and 32 outputs

• 5V power budget: The maximum 5V current supplied by each CPU is listed in Table 1-2. Total current of all expansion modules in the system cannot exceed this budget. See Section 2.5 for further information on power considerations.

Table 1-3 shows the maximum I/O configuration allowed for each S7-200 CPU.

| 5 VDC C | CPU 22x<br>urrent Supplied<br>ansion I/O - ma | Expansion Module<br>5 VDC Current Consumption - ma |     |

|---------|-----------------------------------------------|----------------------------------------------------|-----|

| CPU 222 | 340                                           | EM 221 DI8 x DC24V                                 | 30  |

| CPU 224 | 660                                           | EM 222 DO8 x DC24V                                 | 50  |

| CPU 226 | 1000                                          | EM 222 DO8 x Rly                                   | 40  |

|         |                                               | EM 223 DI4/DO4 x DC24V                             | 40  |

|         |                                               | EM 223 DI4/DO4 x DC24V/Rly                         | 40  |

|         |                                               | EM 223 DI8/DO8 x DC24V                             | 80  |

|         |                                               | EM 223 DI8/DO8 x DC24V/Rly                         | 80  |

|         |                                               | EM 223 DI16/DO16 x DC24V                           | 160 |

|         |                                               | EM 223 DI16/DO16 x DC24V/Rly                       | 150 |

|         |                                               | EM 231 Al4 x 12 Bit                                | 20  |

|         |                                               | EM 231 Al4 x Thermocouple                          | 60  |

|         |                                               | EM 231 AI4 x RTD                                   | 60  |

|         |                                               | EM 232 AQ2 x 12 Bit                                | 20  |

|         |                                               | EM 235 Al4I/AQ1 x 12 Bit                           | 30  |

|         |                                               | EM 277 PROFIBUS-DP                                 | 150 |

#### Table 1-2 Current Supplied by S7-200 CPU

| Module                                                                                                         | 5V ma                                   | Digital<br>Inputs           | Digital<br>Outputs          | Analog<br>Inputs | Analog<br>Outputs |

|----------------------------------------------------------------------------------------------------------------|-----------------------------------------|-----------------------------|-----------------------------|------------------|-------------------|

| CPU 221                                                                                                        | No exp                                  | ansion possible             | е                           |                  |                   |

| CPU 222                                                                                                        |                                         |                             |                             |                  |                   |

| Max Digital In/Out<br>CPU<br>2 x EM 223 DI16/DO16 x DC24V<br>or<br>2 x EM 223 DI16/DO16 x DC24V/Rly            | +340<br>-320 or<br>-300<br><b>&gt;0</b> | 8<br>32                     | 6<br>32                     |                  |                   |

| Total =<br>Max Analog In<br>CPU<br>2 x EM 235 AI4/AQ1<br>Total =                                               | +340<br>-60<br>> <b>0</b>               | <b>40</b><br>8<br><b>8</b>  | 38<br>6<br>6                | 8<br>8           | 2<br><b>2</b>     |

| Max Analog Out<br>CPU<br>2 x EM 232 AQ2<br>Total =                                                             | +340<br>-40<br><b>&gt;0</b>             | 8<br><b>8</b>               | 6<br><b>6</b>               | 0<br><b>0</b>    | 4<br><b>4</b>     |

| CPU 224                                                                                                        |                                         |                             |                             |                  |                   |

| Max Digital In/Rly Out<br>CPU<br>4 x EM 223 DI16/DO16 x DC24V/Rly<br>2 x EM 221 DI8 x DC24V<br>Total =         | +660<br>-600<br>-60<br><b>=0</b>        | 14<br>64<br>16<br><b>94</b> | 10<br>64<br><b>74</b>       |                  |                   |

| Max Digital In/DC Out<br>CPU<br>4 x EM 223 DI16/DO16 x DC24V<br>Total =                                        | +660<br>-640<br><b>&gt;0</b>            | 14<br>64<br><b>78</b>       | 10<br>64<br><b>74</b>       |                  |                   |

| Digital In/Max Rly Out<br>CPU<br>4 x EM 223 DI16/DO16 x DC24V/Rly<br>1 x EM 222 DO8 x Rly<br>Total =           | +660<br>-600<br>-40<br><b>&gt;0</b>     | 14<br>64<br><b>78</b>       | 10<br>64<br>8<br><b>82</b>  |                  |                   |

| CPU 226                                                                                                        |                                         |                             |                             |                  |                   |

| Max Digital In/Rly Out<br>CPU<br>6 x EM 223 DI16/DO16 x DC24V/Rly<br>1 x EM 223 DI8/DO8 x DC24V/Rly<br>Total = | +1000<br>-900<br>-80<br><b>&gt;0</b>    | 24<br>96<br>8<br><b>128</b> | 16<br>96<br>8<br><b>120</b> |                  |                   |

| Max Digital In/DC Out<br>CPU<br>6 x EM 223 DI16/DO16 x DC24V<br>1 x EM 221 DI8 x DC24V<br>Total =              | +1000<br>-960<br>-30<br><b>&gt;0</b>    | 24<br>96<br>8<br><b>128</b> | 16<br>96<br><b>112</b>      |                  |                   |

| CPU 224 or CPU 226                                                                                             |                                         |                             |                             |                  |                   |

| Max Analog In<br>CPU<br>7 x EM 235 AI4/AQ1<br>Total =                                                          | >660<br>-210<br><b>&gt;0</b>            | 14 (24)<br><b>14 (24)</b>   | 10 (16)<br><b>10 (16)</b>   | 28<br><b>28</b>  | 7<br>7            |

| Max Analog Out<br>CPU<br>7 x EM 232 AQ2<br>Total =                                                             | >660<br>-140<br><b>&gt;0</b>            | 14 (24)<br><b>14 (24)</b>   | 10 (16)<br><b>10 (16)</b>   | 0<br><b>0</b>    | 14<br><b>14</b>   |

| Table 1-3 | Maximum I/O Configurations for S7-200 CPUs |

|-----------|--------------------------------------------|

|-----------|--------------------------------------------|

## Installing an S7-200 PLC

The installation of the S7-200 equipment is designed to be easy. You can use the mounting holes to attach the modules to a panel, or you can use the built-in clips to mount the modules onto a standard (DIN) rail. The small size of the S7-200 allows you to make efficient use of space.

This chapter provides guidelines for installing and wiring your S7-200 system.

#### **Chapter Overview**

| Section | Description                                                     | Page |

|---------|-----------------------------------------------------------------|------|

| 2.1     | Panel Layout Considerations                                     | 2-2  |

| 2.2     | Installing and Removing an S7-200 Micro PLC or Expansion Module | 2-6  |

| 2.3     | Installing the Field Wiring                                     | 2-9  |

| 2.4     | Using Suppression Circuits                                      | 2-16 |

| 2.5     | Power Considerations                                            | 2-18 |

#### 2.1 Panel Layout Considerations

#### Installation Configuration

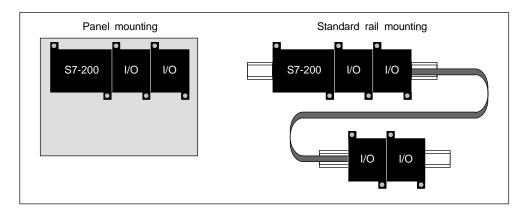

You can install an S7-200 either on a panel or on a standard rail. You can mount the S7-200 either horizontally or vertically. You can connect the S7-200 to expansion modules by one of these methods:

- A flexible ribbon cable with mating connector is built into the I/O module for easy connection to the PLC or another expansion module.

- An I/O expansion cable is also available to add flexibility to your mounting configuration.

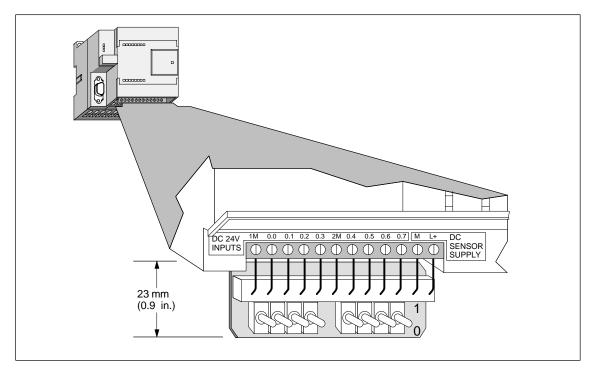

Figure 2-1 shows a typical configuration for these types of installations.

Figure 2-1 Mounting Configurations

#### **Clearance Requirements for Installing an S7-200 PLC**

Use the following guidelines as you plan your installation:

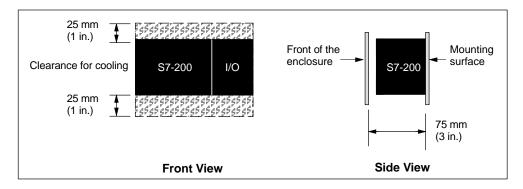

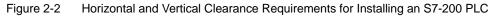

- The S7-200 CPU and expansion modules are designed for natural convection cooling. You must provide a clearance of at least 25 mm (1 in.), both above and below the units, for proper cooling. See Figure 2-2. Continuous operation of all electronic products at maximum ambient temperature and load reduces their life.

- For vertical mounting, the maximum ambient temperature is reduced by 10° C. The CPU should be mounted below any expansion modules. If you are mounting on a vertical DIN rail, you should use the DIN rail stop.

- Allow 75 mm (3 in.) for mounting depth. See Figure 2-2.

- Be sure to allow enough space in your mounting design to accommodate the I/O wiring and communication cable connections.

#### **Standard Rail Requirements**

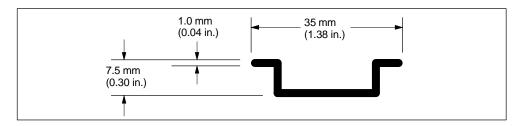

The S7-200 CPU and expansion modules can be installed on a standard (DIN) rail (DIN EN 50 022). Figure 2-3 shows the dimensions for this rail.

Figure 2-3 Standard Rail Dimensions

#### **Panel-Mounting Dimensions**

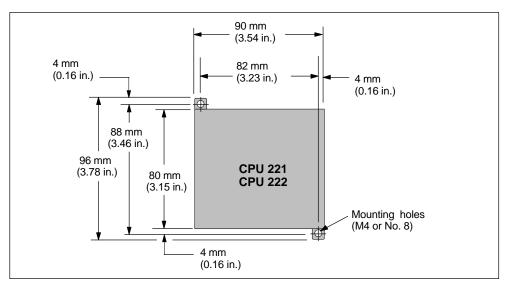

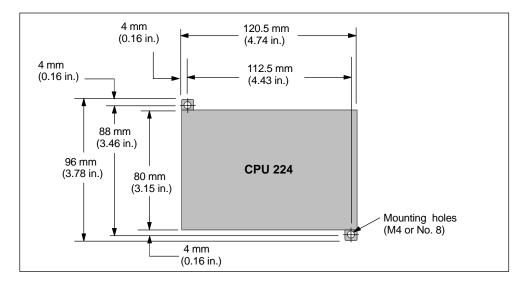

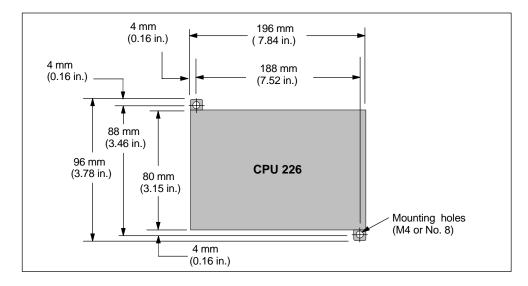

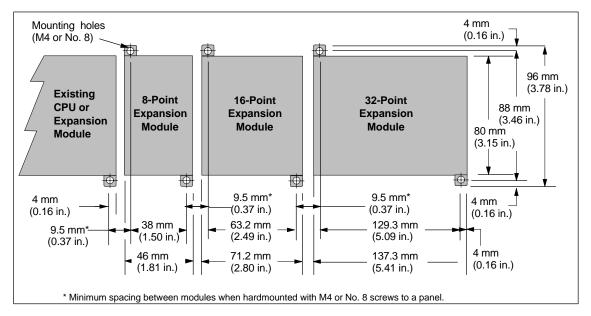

S7-200 CPUs and expansion modules include mounting holes to facilitate installation on panels. Figure 2-4 through Figure 2-7 provide the mounting dimensions for the different S7-200 CPUs and expansion modules.

Figure 2-4 Mounting Dimensions for CPU 221 and CPU 222

Figure 2-5 Mounting Dimensions for a CPU 224

Figure 2-6 Mounting Dimensions for a CPU 226

Figure 2-7 Mounting Dimensions for Expansion Modules

#### 2.2 Installing and Removing an S7-200 Micro PLC or Expansion Module

#### Mounting an S7-200 Micro PLC or Expansion Module onto a Panel

#### Warning

Attempts to install or remove S7-200 CPUs or related equipment with power applied could cause electric shock or faulty operation of equipment.

Failure to disable all power to the S7-200 and related equipment during installation or removal procedures may result in death or serious personal injury, and/or damage to equipment.

Always follow appropriate safety precautions and ensure that power to the S7-200 is disabled before attempting to install or remove S7-200 CPUs or related equipment.

Use the following procedure for installing an S7-200 CPU onto a panel:

- Locate, drill, and tap the mounting holes for DIN M4 or American Standard number 8 screws. Refer to Section 2.1 for mounting dimensions and other considerations.

- 2. Secure the S7-200 CPUs onto the panel, using DIN M4 or American Standard number 8 screws.

To install the expansion module onto a panel, follow these steps:

- 1. Locate, drill, and tap the mounting holes for DIN M4 or American Standard number 8 screws. Refer to Section 2.1 for mounting dimensions and other considerations.

- 2. Place the I/O module next to the PLC or expansion module and secure it.

- 3. Plug the expansion module ribbon cable into the CPU connector under the front access door. The cable is keyed for correct orientation.

Installation is complete.

#### Installing an S7-200 Micro PLC or Expansion Module onto a Standard Rail

#### Warning

Attempts to install or remove S7-200 CPUs or related equipment when they are powered up could cause electric shock or faulty operation of equipment.

Failure to disable all power to the S7-200 CPUs and related equipment during installation or removal procedures may result in death or serious personal injury, and/or damage to equipment.

Always follow appropriate safety precautions and ensure that power to the S7-200 is disabled before attempting to install or remove S7-200 CPUs or related equipment.

To install the S7-200 CPU onto a standard rail, follow these steps:

- 1. Secure the rail to the mounting panel every 75 mm (3.0 in.).

- 2. Snap open the clip (located on the bottom of the S7-200) and hook the back of the S7-200 onto the rail.

- 3. Snap the clip closed, carefully checking to ensure that the clip has fastened the S7-200 securely onto the rail.

To install the expansion module onto a standard rail, use the following steps:

- 1. Snap open the clip and hook the back of the expansion module onto the rail next to the CPU or expansion module.

- 2. Snap the clip closed to secure the expansion module to the rail. Carefully check to ensure that the clip has fastened the module securely onto the rail.

- 3. Plug the expansion module ribbon cable into the CPU connector under the front access door. The cable is keyed for correct orientation.

- 4. Installation is complete.

#### Note

Modules in an environment with high vibration potential or modules that have been installed in a vertical position may require DIN rail stops.

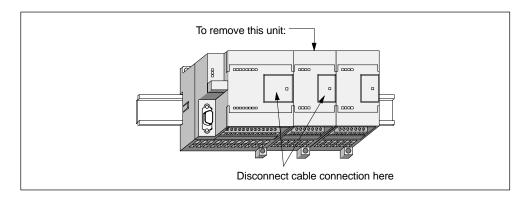

#### Removing the S7-200 Micro PLC or Expansion Module

#### Warning

Attempts to install or remove S7-200 CPUs or related equipment when they are powered up could cause electric shock or faulty operation of equipment.

Failure to disable all power to the S7-200 CPUs and related equipment during installation or removal procedures may result in death or serious personal injury, and/or damage to equipment.

Always follow appropriate safety precautions and ensure that power to the S7-200 modules is disabled before installation.

To remove the S7-200 CPU or expansion module, follow these steps:

- 1. Disconnect all the wiring and cabling that is attached to the module that you are removing. See Figure 2-8. Some CPUs and expansion modules have removeable connectors.

- 2. Open the front access door and disconnect the ribbon cable from the adjacent modules.

- 3. Unscrew the mounting screws or snap open the clip, and remove the module.

#### Warning

If you install an incorrect module, the program in the micro PLC could function unpredictably.

Failure to replace an expansion module and expansion cable with the same model or in the proper orientation may result in death or serious personal injury, and/or damage to equipment.

Replace an expansion module with the same model, and orient it correctly.

Figure 2-8 Removing the Expansion Module

#### 2.3 Installing the Field Wiring

#### Warning

Attempts to install or remove S7-200 CPUs or related equipment when they are powered up could cause electric shock or faulty operation of equipment.

Failure to disable all power to the S7-200 CPUs and related equipment during installation or removal procedures may result in death or serious personal injury, and/or damage to equipment.

Always follow appropriate safety precautions and ensure that power to the S7-200 is disabled before installing field wiring.

#### General Guidelines

The following items are general guidelines for designing the installation and wiring of your S7-200 Micro PLC:

- Ensure that you follow all applicable electrical codes when wiring the S7-200 Micro PLC. Install and operate all equipment according to all applicable national and local standards. Contact your local authorities to determine which codes and standards apply to your specific case.

- Always use the proper wire size to carry the required current. The S7-200 accepts wire sizes from 1.50 mm<sup>2</sup> to 0.50 mm<sup>2</sup> (14 AWG to 22 AWG).

- Ensure that you do not over-tighten the connector screws. The maximum torque is 0.56 N-m (5 inch-pounds).

- Always use the shortest wire possible (maximum 500 m shielded, 300 m unshielded). Wiring should be run in pairs, with a neutral or common wire paired with a hot or signal-carrying wire.

- Separate AC wiring and high-energy, rapidly switched DC wiring from low-energy signal wiring.

- Properly identify and route the wiring to the S7-200, using strain relief for the wiring as required. For more information about identifying the terminals, see the specifications in Appendix A.

- Install appropriate surge suppression devices for any wiring that is subject to lightning surges.

- External power should not be applied to an output load in parallel with a DC output point. This may cause reverse current through the output, unless a diode or other barrier is provided in the installation.

#### Warning

Control devices can fail in an unsafe condition, resulting in unexpected operation of controlled equipment.

Such unexpected operations could result in death or serious personal injury, and/or equipment damage.

Consider using an emergency stop function, electromechanical overrides, or other redundant safeguards that are independent of the programmable controller.

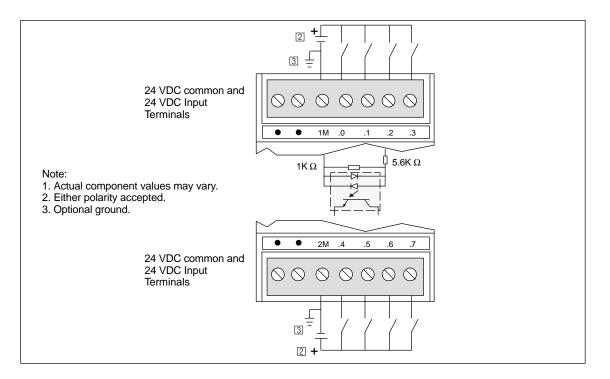

#### Grounding and Circuit Reference Point Guidelines for Using Isolated Circuits

The following items are grounding and circuit guidelines for using isolated circuits:

- You should identify the reference point (0 voltage reference) for each circuit in the installation, and the points at which circuits with possibly different references can connect together. Such connections can result in unwanted current flows that can cause logic errors or damage circuits. A common cause of different reference potentials is grounds that are physically separated by long distances. When devices with widely separated grounds are connected with a communication or sensor cable, unexpected currents can flow through the circuit created by the cable and the ground. Even over short distances, load currents of heavy machinery can cause differences in ground potential or can directly induce unwanted currents by electromagnetic induction. Power supplies that are improperly referenced with respect to each other can cause damaging currents to flow between their associated circuits.

- When you connect CPUs with different ground potentials to the same PPI network, you should use an isolated RS-485 repeater.

- S7-200 products include isolation boundaries at certain points to help prevent unwanted current flows in your installation. When you plan your installation, you should consider where these isolation boundaries are provided, and where they are not provided. You should also consider the isolation boundaries in associated power supplies and other equipment, and where all associated power supplies have their reference points.

- You should choose your ground reference points and use the isolation boundaries provided to interrupt unneeded circuit loops that could allow unwanted currents to flow. Remember to consider temporary connections that may introduce a new circuit reference, such as the connection of a programming device to the CPU.

- When locating grounds, you must also consider safety grounding requirements and the proper operation of protective interrupting devices.

- In most installations, you will have the best noise immunity if you connect the sensor supply M terminal to ground.

The following descriptions are an introduction to general isolation characteristics of the S7-200 family, but some features may be different on specific products. Consult your product specifications in Appendix A for information about which circuits include isolation boundaries and the ratings of the boundaries. Isolation boundaries rated less than 1,500 VAC are designed as functional isolation only, and should not be depended on as safety boundaries.

- Logic circuit reference is the same as DC sensor supply M.

- Logic circuit reference is the same as the input power supply M on a CPU with DC power supply.

- CPU communication ports have the same reference as logic circuit.

- Analog inputs and outputs are not isolated from logic circuit. Analog inputs are full differential to provide low voltage common mode rejection.

- Logic circuit is isolated from ground to 500 VAC.

- DC digital inputs and outputs are isolated from logic circuit to 500 VAC.

- DC digital I/O groups are isolated from each other by 500 VAC.

- Relay outputs are isolated from logic circuit to 1,500 VAC.

- Relay output groups are isolated from each other by 1,500 VAC.

- AC power supply line and neutral are isolated from ground, the logic circuit, and all I/O to 1,500 VAC.

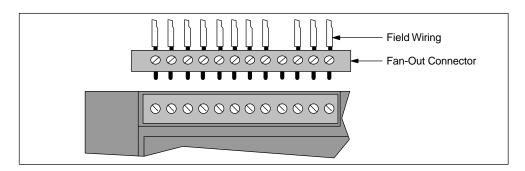

## Using the Optional Field Wiring Connector for Units Without a Removable Connector

The optional field wiring fan-out connector (Figure 2-9) allows for field wiring connections to remain fixed when you remove and re-install the S7-200 unit. Refer to Appendix E for the order number of the fan-out connector.

Figure 2-9 Optional Field Wiring Connector

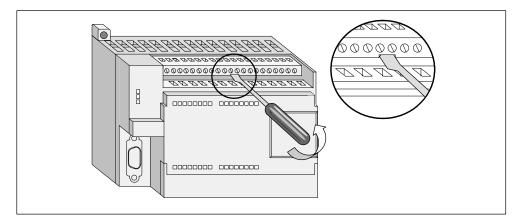

#### Using the Removable Terminal Block Connector

The removable terminal block connector (Figure 2-10) allows field wiring connections to remain fixed when you remove and re-install the S7-200 CPU and I/O expansion modules.

To remove the terminal block connector from the CPU or expansion module, follow these steps:

- 1. Raise the top terminal door of the CPU or expansion module.

- 2. Insert a screwdriver in the notch in the middle of the terminal block as shown in Figure 2-10.

- 3. Press down firmly and pry out the terminal connector as shown below.

To reinstall a terminal block connector in a CPU or expansion module, follow these steps:

- 1. Raise the top terminal door of the CPU or expansion module.

- 2. Ensure that the new terminal block connector is properly aligned with the pins on the CPU or expansion module.

- 3. Press down the terminal block connector into the CPU or expansion module until the connector snaps into place.

Figure 2-10 Removable Terminal Block Connector for the CPU 224 and I/O Expansion Modules.

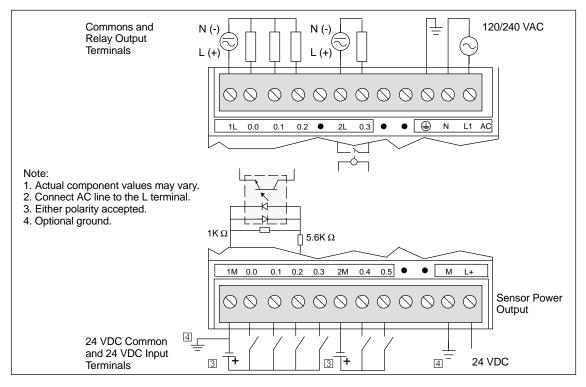

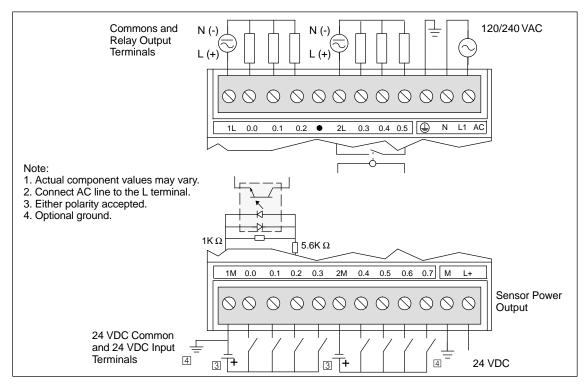

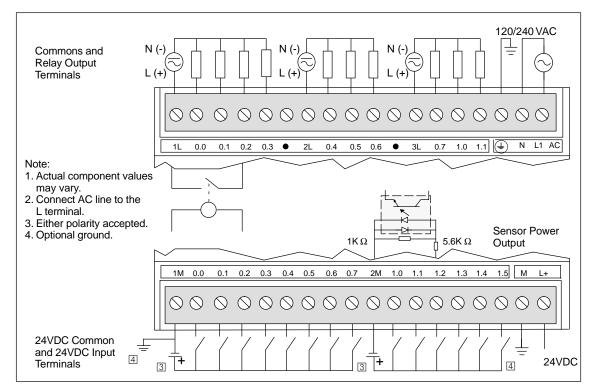

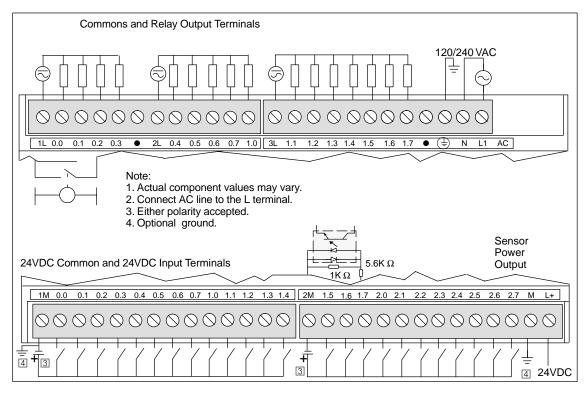

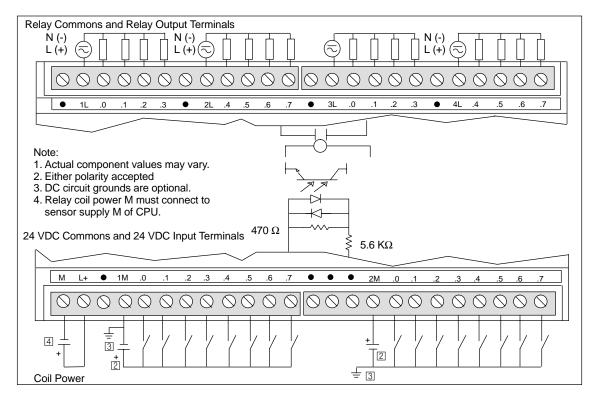

#### **Guidelines for AC Installation**

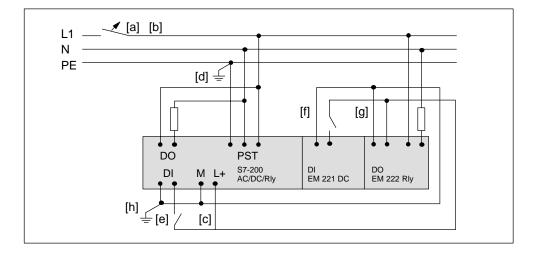

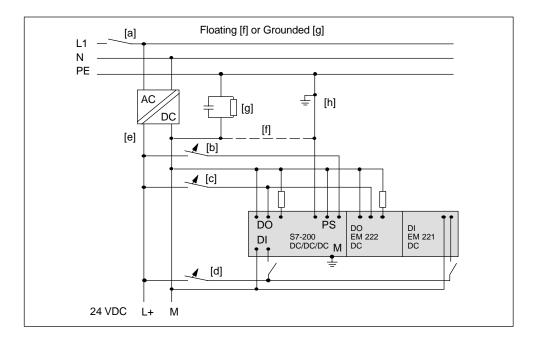

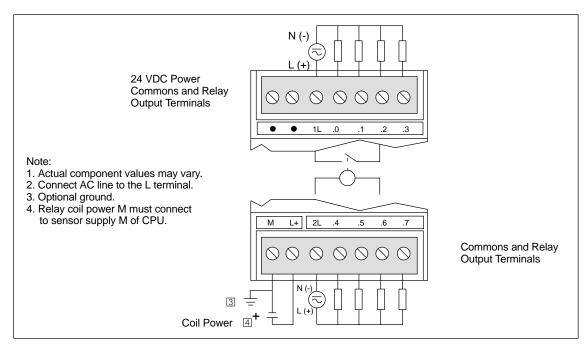

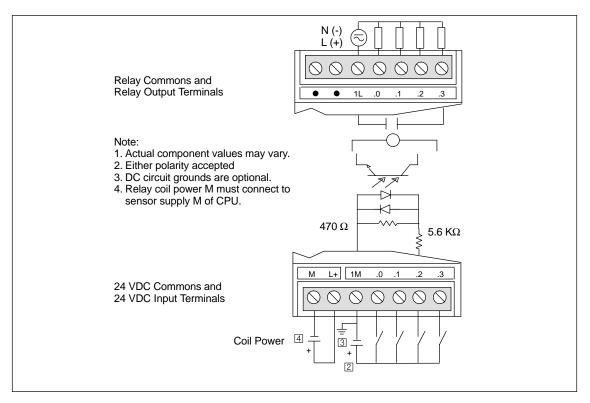

The following items are general wiring guidelines for AC installations. Refer to Figure 2-11.

[a] Provide a single disconnect switch that removes power from the CPU, all input circuits, and all output (load) circuits.

[b] Provide overcurrent devices to protect the CPU power supply, the output points, and the input points. You can also fuse each output point individually for greater protection.

[c] External overcurrent protection for input points is not required when you use the 24 VDC sensor supply from the Micro PLC. This sensor supply is short-circuit protected.

[d] Connect all S7-200 ground terminals to the closest available earth ground to provide the highest level of noise immunity. It is recommended that all ground terminals be connected to a single electrical point. Use 14 AWG or 1.5  $mm^2$  wire for this connection.

[e] DC sensor supply from the CPU may be used for CPU inputs,

[f] expansion DC inputs, and [g] expansion relay coils. This sensor supply is short-circuit protected.

[h] In most installations, you will have the best noise immunity if you connect the sensor supply M terminal to ground.

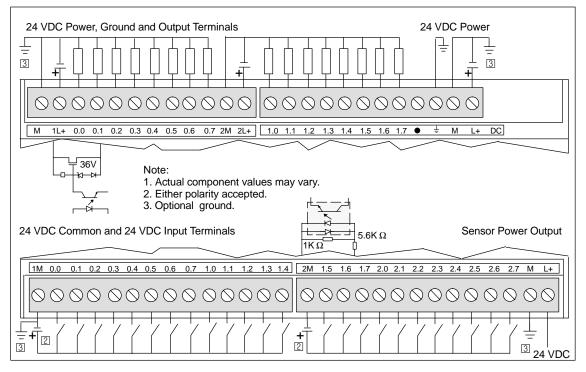

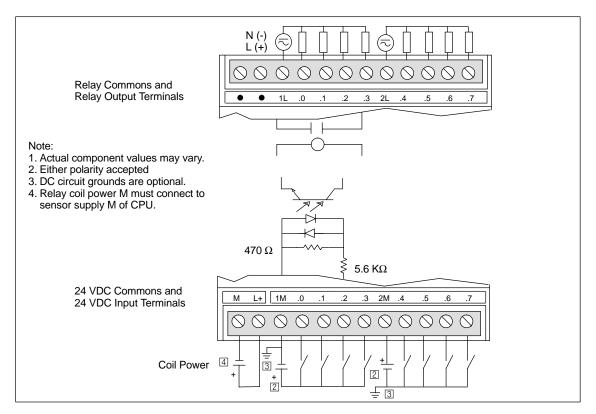

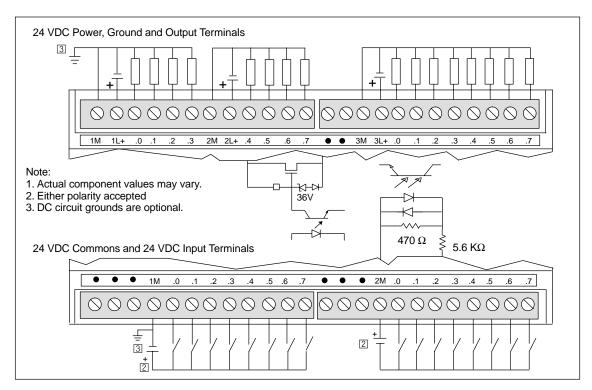

Figure 2-11 120 VAC/230 VAC Using a Single Overcurrent Switch to Protect the CPU and Load Wiring

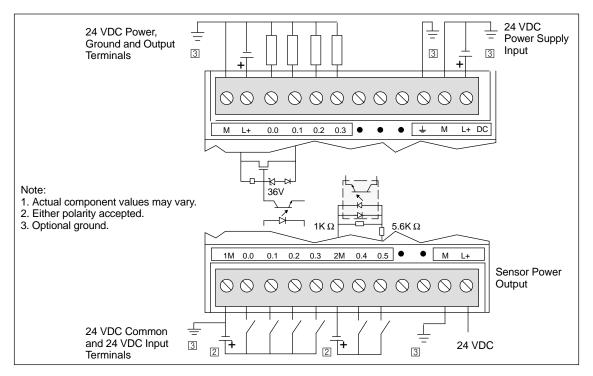

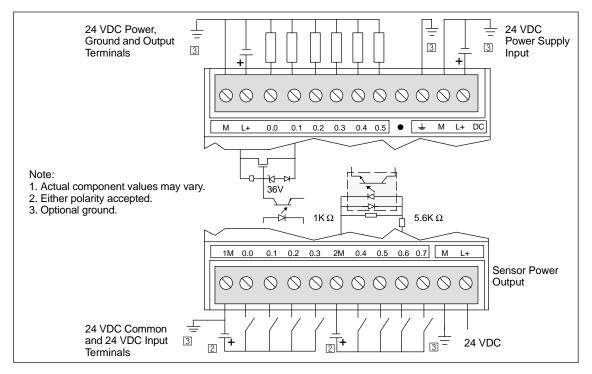

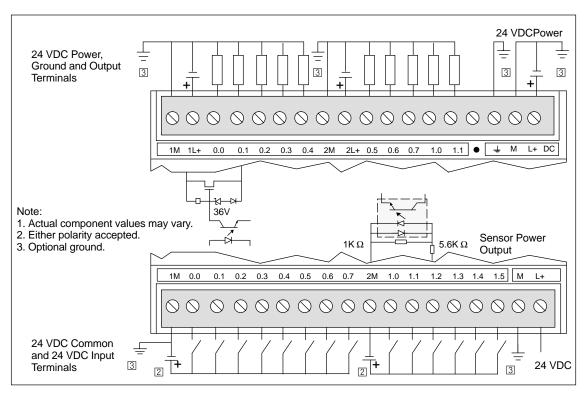

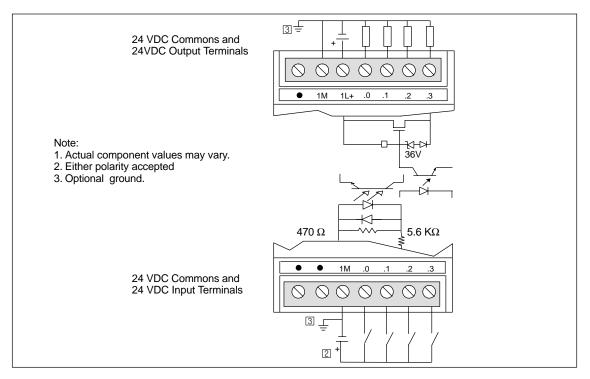

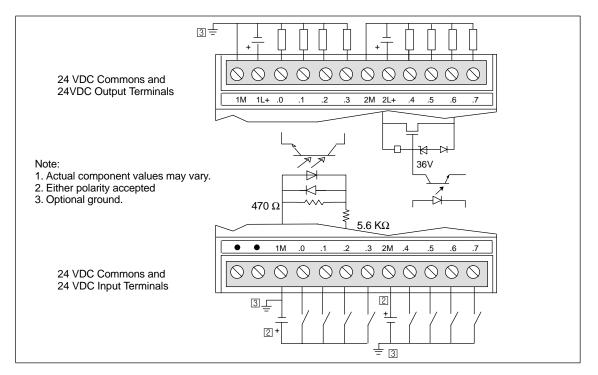

#### **Guidelines for DC Installation**

The following items are general wiring guidelines for DC installations. Refer to Figure 2-12.

[a] Provide a single disconnect switch that removes power from the CPU, all input circuits, and all output (load) circuits.

[b] Provide overcurrent devices to protect the CPU power supply, [c] the output points, and [d] the input points. You can also fuse each output point individually for greater protection. External overcurrent protection for input points is not required when you use the 24 VDC sensor supply from the Micro PLC. This sensor supply is current limited internally.

[e] Ensure that the DC power supply has sufficient surge capacity to maintain voltage during sudden load changes. External capacitance may be required.

[f] In most installations, you will have best noise immunity by connecting all DC power supplies to ground. Equip ungrounded DC power supplies with a resistor and a capacitor in parallel [g] from the power source common to protective earth ground. The resistor provides a leakage path to prevent static charge accumulations, and the capacitor provides a drain for high frequency noise. Typical values are 1 M $\Omega$  and 4,700 pf.

[h] Connect all S7-200 ground terminals to the closest available earth ground to provide the highest level of noise immunity. It is recommended that all ground terminals be connected to a single electrical point. Use 14 AWG or 1.5 mm<sup>2</sup> wire for this connection.

Always supply 24 VDC circuits from a source that provides safe electrical separation from 120/230 VAC power and similar hazards.

The following documents provide standard definitions of safe separation:

- PELV (protected extra low voltage) according to EN60204-1

- Class 2 or Limited Voltage/Current Circuit according to UL 508

Figure 2-12 DC System Installation

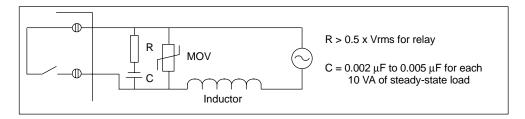

#### 2.4 Using Suppression Circuits

#### **General Guidelines**

Equip inductive loads with suppression circuits that limit voltage rise on loss of power. Use the following guidelines to design adequate suppression. The effectiveness of a given design depends on the application, and you must verify it for a particular use. Be sure all components are rated for use in the application.

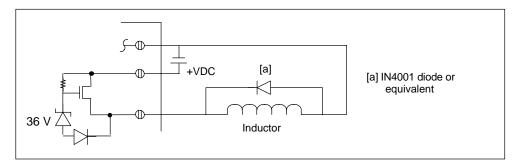

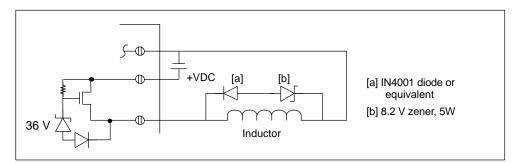

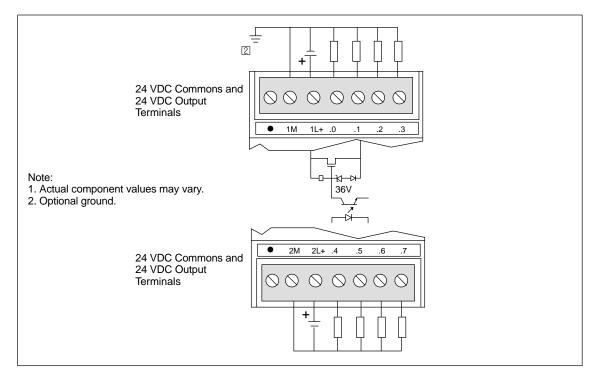

#### **Protecting DC Transistors**

The S7-200 DC transistor outputs include zener-controlled clamping that is adequate for many installations. Use external suppression diodes for either large or frequently switched inductive loads to prevent overpowering the internal circuits. Figure 2-13 and Figure 2-14 show typical applications for DC transistor outputs.

Figure 2-13 Diode Suppression for DC Transistor Outputs

Figure 2-14 Zener Diode Suppression for DC Transistor Outputs

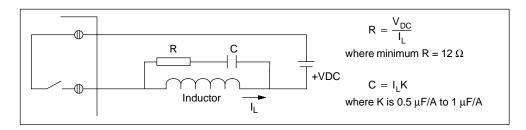

#### **Protecting Relays That Control DC Power**

Resistor/capacitor networks, as shown in Figure 2-15, can be used for low voltage (30 V) DC relay applications. Connect the network across the load.

Figure 2-15 Resistor/Capacitor Network on Relay-Driven DC Load

You can also use diode suppression, as shown in Figure 2-13 and Figure 2-14, for DC relay applications. A threshold voltage of up to 36 V is allowed if you use a reverse zener diode.

#### **Protecting Relays That Control AC Power**

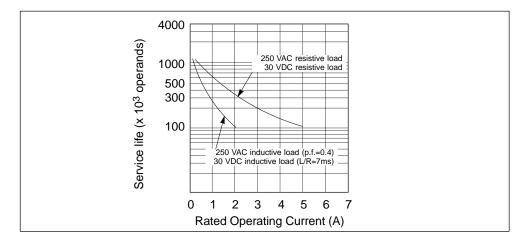

When you use a relay to switch 115 VAC/230 VAC inductive loads, you should place resistor/capacitor networks across the relay contacts as shown in Figure 2-16. You can also use a metal oxide varistor (MOV) to limit peak voltage. Ensure that the working voltage of the MOV is at least 20% greater than the nominal line voltage.

Figure 2-16 AC Load with Network across Relay

The capacitor allows leakage current to flow around the open switch. Be sure that the leakage current, I (leakage) =  $2 \times 3.14 \times f \times C \times Vrms$ , is acceptable for the application.

For example: A NEMA size 2 contactor lists 183 VA coil inrush and 17 VA sealed coil load. At 115 VAC, the inrush current is 183 VA/115 V = 1.59 A, which is within the 2-A switching capability of the relay contacts.

The resistor =  $0.5 \times 115 = 57.5 \Omega$ ; choose  $68 \Omega$  as a standard value. The capacitor =  $(17 \text{ VA}/10) \times 0.005 = 0.0085 \mu\text{F}$ ; choose  $0.01 \mu\text{F}$  as the value. The leakage current =  $2 \times 3.14 \times 60 \times 0.01 \times 10^{-6} \times 115 = 0.43 \text{ mA rms}$ .

#### 2.5 Power Considerations

The S7-200 CPUs have an internal power supply that provides power for the CPU, the expansion modules, and other 24 VDC user power requirements. Use the following information as a guide for determining how much power (or current) the CPU can provide for your configuration.

#### **Power Requirements**

Each S7-200 CPU supplies both 5 VDC and 24 VDC power:

- Each CPU has a 24 VDC sensor supply that can supply 24 VDC for local input points or for relay coils on the expansion modules. If the power requirement for 24 VDC exceeds the power budget of the CPU, you can add an external 24 VDC power supply to provide 24 VDC to the expansion modules. You must manually connect the 24 VDC supply to the input points or relay coils.

- The CPU also provides 5 VDC power for the expansion modules when an expansion module is connected. If the 5 VDC power requirements for expansion modules exceeds the power budget of the CPU, you must remove expansion modules until the requirement is within the power budget.

The specifications in Appendix A provide information about the power budgets of the CPUs and the power requirements of the expansion modules.

#### Warning

Connecting an external 24 VDC power supply in parallel with the S7-200 DC Sensor Supply can result in a conflict between the two supplies as each seeks to establish its own preferred output voltage level.

The result of this conflict can be shortened lifetime or immediate failure of one or both power supplies, with consequent unpredictable operation of the PLC system. Unpredictable operation could result in death or serious injury to personnel, and/or damage to equipment and property.

The S7-200 DC Sensor Supply and any external power supply should provide power to different points. A single connection of the commons is allowed.

#### **Calculating a Sample Power Requirement**

Table 2-1 shows a sample calculation of the power requirements for an S7-200 Micro PLC that includes the following:

- CPU 224 AC/DC/Relay

- 3 each EM 223 8 DC In/8 Relay Out

- 1 each EM 221 8 DC In

This installation has a total of 46 inputs and 34 outputs.

The CPU in this example provides sufficient 5 VDC current for the expansion modules, but does not provide enough 24 VDC current from the sensor supply for all of the inputs and expansion relay coils. The I/O requires 400 mA and the CPU provides only 280 mA. This installation requires an additional source of at least 120 mA at 24 VDC power to operate all the included 24 VDC inputs and outputs.

Table 2-1 Power Budget Calculations for a Sample Configuration

| CPU Power Budget    | 5 VDC  | 24 VDC |

|---------------------|--------|--------|

| CPU 224 AC/DC/Relay | 660 mA | 280 mA |

minus

| System Requirements          | 5 VDC       |        | 24 VDC         |        |

|------------------------------|-------------|--------|----------------|--------|

| CPU 224, 14 inputs           |             |        | 14 * 4 mA =    | 56 mA  |

| 3 EM 223, 5 V power required | 3 * 80 mA = | 240 mA |                |        |

| 1 EM 221, 5V power required  | 1 * 30 mA = | 30 mA  |                |        |

| 3 EM 223, 8 inputs each      |             |        | 3 * 8 * 4 mA = | 96 mA  |

| 3 EM 223, 8 relay coils each |             |        | 3 * 8 * 9 mA = | 216 mA |

| 1 EM 221, 8 inputs each      |             |        | 8 * 4 mA =     | 32 mA  |

| Total Requirements           |             | 270 mA |                | 400 mA |

equals

| Current Balance 5 VDC |        | 24 VDC   |  |

|-----------------------|--------|----------|--|

| Current Balance Total | 390 mA | [120 mA] |  |

#### **Calculating Your Power Requirement**

Use the table below to determine how much power (or current) the CPU can provide for your configuration. Refer to Appendix A for the power budgets of your CPU and the power requirements of your expansion modules.

| Power Budget | 5 VDC | 24 VDC |

|--------------|-------|--------|

|              |       |        |

minus

| System Requirements | 5 VDC | 24 VDC |

|---------------------|-------|--------|

|                     |       |        |

|                     |       |        |

|                     |       |        |

|                     |       |        |

|                     |       |        |

|                     |       |        |

|                     |       |        |

| Total Requirements  |       |        |

equals

| Current Balance       | 5 VDC | 24 VDC |

|-----------------------|-------|--------|

| Current Balance Total |       |        |

# 3

### Getting Started with an S7-200 Programming System

This chapter describes how to set up an S7-200 programming system. The S7-200 programming system described in this chapter consists of:

- An S7-200 CPU

- A PC or programming device with STEP 7-Micro/WIN 32 installed

- An interconnecting cable

#### **Chapter Overview**

| Section | Description                                               |      |

|---------|-----------------------------------------------------------|------|

| 3.1     | Overview                                                  | 3-2  |

| 3.2     | Quick Start for STEP 7-Micro/WIN 32                       | 3-3  |

| 3.3     | How Do I Set Up Communications Using the PC/PPI Cable?    | 3-5  |

| 3.4     | How Do I Complete the Communications Connection?          | 3-9  |

| 3.5     | How Do I Change the Communications Parameters for My PLC? | 3-10 |

#### 3.1 Overview

#### **General Information**

You will need to base your installation on the following criteria:

- The operating system that you are using (Windows 95, Windows 98, or Windows NT 4.0)

- The type of hardware that you are using, for example:

- PC with PC/PPI cable

- PC or SIMATIC programming device with communications processor (CP) card

- CPU 221, CPU 222, CPU 224, CPU 226

- Modem

- The baud rate that you are using

#### **Recommended Equipment**

STEP 7-Micro/WIN 32, version 3.1, and STEP 7-Micro/WIN 32 Toolbox are Windows-based software applications that support the 32-bit Windows 95, Windows 98, and Windows NT environments. In order to use these software programs, the following equipment is recommended:

- TP070 Touch Panel for use with STEP 7-Micro/WIN 32 Toolbox

- A personal computer (PC) with an 80586 or greater processor and 16 Mbytes of RAM, or a Siemens programming device with STEP 7-Micro/WIN 32 installed (such as a PG 740). The minimum computer requirement is an 80486 processor with 8 Mbytes.

- One of the following sets of equipment:

- A PC/PPI cable connected to your communications port

- A communications processor (CP) card

- VGA monitor, or any monitor supported by Microsoft Windows with 1024 X 768 resolution

- At least 50 Mbytes of free hard disk space

- Windows 95, Windows 98, or Windows NT 4.0

- Optional but recommended: any mouse supported by Microsoft Windows

STEP 7-Micro/WIN 32 provides extensive online help and an online *Getting Started Manual*. Use the **Help** menu command or press F1 to obtain the most current information.

STEP 7-Micro/WIN 32 Toolbox also provides the TP070 Configuration Software for configuring the TP070 touch Panel, and the USS Protocol Instructions for use with MicroMaster Drives.

#### 3.2 Quick Start for STEP 7-Micro/WIN 32

#### **Pre-Installation Instructions**

Before running the setup procedure, do the following:

- If a previous version of STEP 7-Micro/WIN 32 is installed, back up all STEP 7-Micro/WIN projects to diskette.

- Make sure all applications are closed, including the Microsoft Office toolbar.

- Be sure the cable between your personal computer and the CPU is connected. See Section 3.3 for instructions.

#### Installing STEP 7-Micro/WIN 32

Use the following procedure to install the STEP 7-Micro/WIN 32 software:

- 1. Start by inserting the CD or disk in the CD or disk drive of your computer.

- 2. Click once on the "Start" button to open the Windows menu.

- 3. Click on the Run... menu item.

- 4. If you are installing from a diskette: In the "Run" dialog box, type a:\setup and click on OK or press ENTER. This starts the setup procedure.

If you are installing from a CD: In the "Run" dialog box, type e:\setup (where "e" is the drive letter of the CD) and click on OK or press ENTER. This starts the setup procedure.

- 5. Follow the online setup procedure to complete the installation.

- 6. The installation will automatically display the "Set the PG/PC Interface" dialog box. The PG/PC interface parameter is set up later in this chapter. Click on Cancel to continue.

- 7. The "Setup Complete" dialog box is now displayed with one of the following options:

- Option 1: Yes, I want to restart my computer now. (default selected)

No, I will restart my computer later

If Option 1 is displayed, it is recommended that you accept the default settings, and select Finish to complete the installation and view the Read Me file for the the most recent information about STEP 7-Micro/WIN 32.

• Option 2: Yes, I want to view the Read Me file now. (default selected) No, I want to launch STEP 7-Micro/WIN 32 now.

If Option 2 is displayed, it is recommended that you accept the default settings and select Finish to complete the installation and view the Read Me file for the most recent information about STEP 7-Micro/WIN 32.

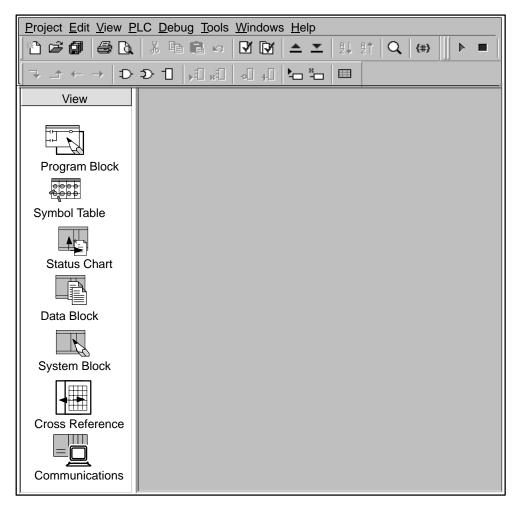

For Option 2: both options can be selected. Selecting Finish with both options selected will complete the installation, display the Read Me file and launch STEP 7-Micro/WIN 32. See Figure 3-1.

Review the READMEX.TXT file included on your CD or diskettes for the most recent information about STEP 7-Micro/WIN 32. (In the *x* position, the letter A = German, B = English, C = French, D = Spanish, E = Italian.)

#### Note

Installing STEP 7-Micro/WIN in the same directory as an existing installation uninstalls the existing installation.

#### **Common Problem List for Single Connection User**

The following situations can cause the communication to fail:

- Wrong baud rate: Correct the baud rate

- Wrong station address: Correct the station address

- PC/PPI cable set incorrectly: Check DIP switch settings on PC/PPI cable

- Wrong communication port on personal computer: Check comm port

- CPU in freeport mode (comm port under control of user program): Put CPU in STOP mode

- Conflict with other masters: Disconnect the CPU from the network.

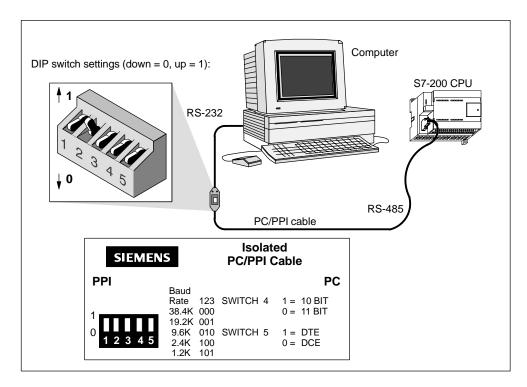

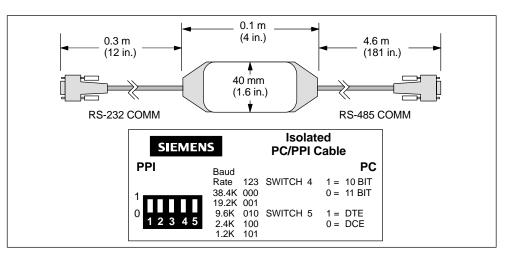

#### 3.3 How Do I Set Up Communications Using the PC/PPI Cable?

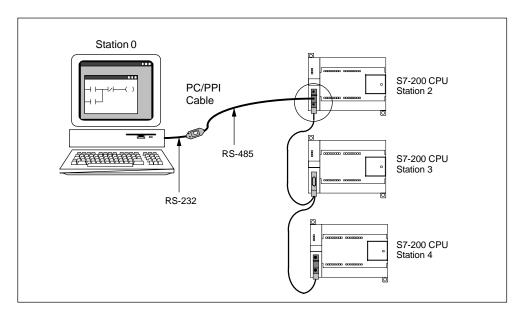

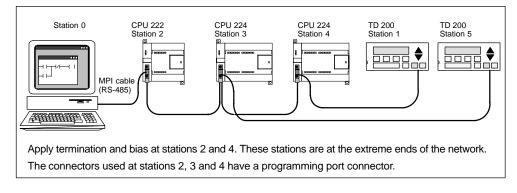

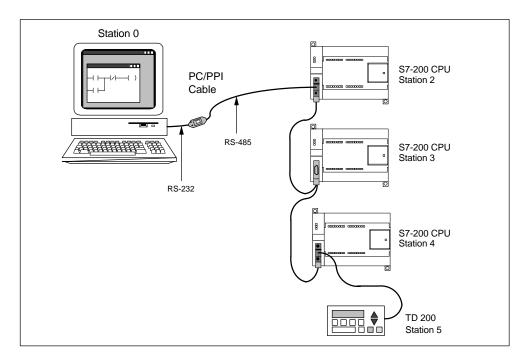

This section explains how to set up communications between an S7-200 CPU and your personal computer using the PC/PPI cable. This is single master configuration with no other hardware (such as a modem or a programming device) installed.

#### How Do I Connect My Computer to the CPU?

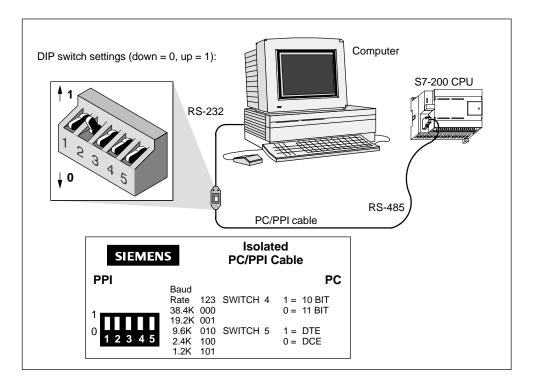

Figure 3-1 shows a typical configuration for connecting your personal computer to your CPU with the PC/PPI cable. To establish proper communications between the components, follow these steps:

- Set the DIP switches on the PC/PPI cable for the baud rate supported by your personal computer. You should also select 11-bit and DCE if these options are supported by your PC/PPI cable.

- 2. Connect the RS-232 end of the PC/PPI cable (labeled PC) to the communications port of your computer, either COM1 or COM2, and tighten the connecting screws.

- 3. Connect the RS-485 end of the PC/PPI cable (labeled PPI) to the communications port of the CPU, and tighten the connecting screws.

For the technical specifications of the PC/PPI cable, see Appendix A; for its order number, see Appendix E. For network applications with multiple connections see Chapter 7.

Figure 3-1 Communicating with a CPU in PPI Mode

#### How Do I Verify the Default Parameters for My Communications Interface?

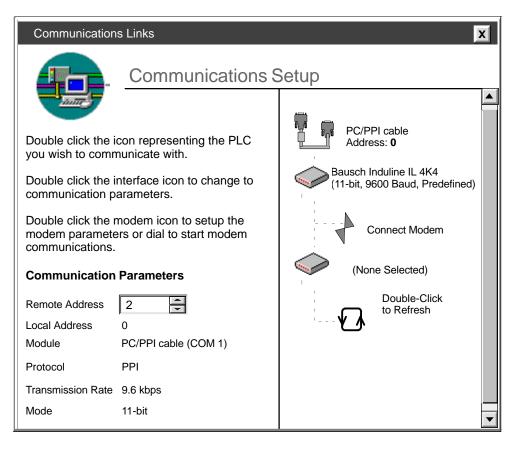

You can verify the default parameters for your interface by following the steps below:

- In the STEP 7-Micro/WIN 32 window, click the Communications icon, or select View > Communications from the menu. The Communications Links dialog box appears.

- 2. In the Communications Links dialog box, double-click on the icon for the PC/PPI cable. The Set the PG/PC Interface dialog box appears. See Figure 3-2.

- 3. Select the "Properties" button. The Properties dialog box for the interface appears (see Figure 3-3). Check the properties to ensure that they are correct. The default transmission rate is 9,600 baud (9.6 kbps).

For help in changing the default parameters, see Section 7.3 in Chapter 7.

#### Note

If the hardware that you are using does not appear on the list shown in "Set the PG/PC Interface" dialog box, then you must install the correct hardware. See Section 7.2.

| Commu                                             | inications Links                                                                                                         | x |

|---------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|---|

|                                                   | Communications Setup                                                                                                     |   |

| Doub<br>you<br>wish t<br>Doub<br>comm             | Set PG/PC Interface (V5.0)                                                                                               |   |

| Doub<br>mode<br>comm                              | Micro/WIN>PC/PPI cable (PPI) (Standard for Micro/WIN) Interface Parameter Assignment Used: PC/PPI cable (PPI) Properties |   |

| Remo<br>Local<br>Modul<br>Protoc<br>Trans<br>Mode | CP5611(PROFIBUS)         CP5611(MPI)           CP5611(PPI)         Copy           CP5611(PROFIBUS)         Copy          |   |

|                                                   | Add/Remove     Select       OK     Cancel                                                                                |   |

Figure 3-2 Set the PG/PC Interface Dialog Box

| Set the PG/PC Interface (V5.0)  | X                  |

|---------------------------------|--------------------|

| Access Path                     |                    |

| Properties - PC/PPI cable (PPI) | ×                  |

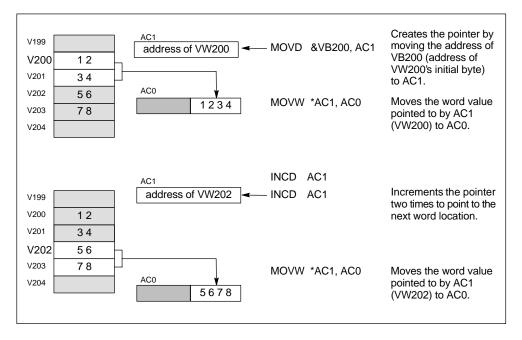

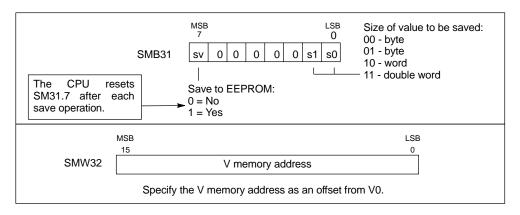

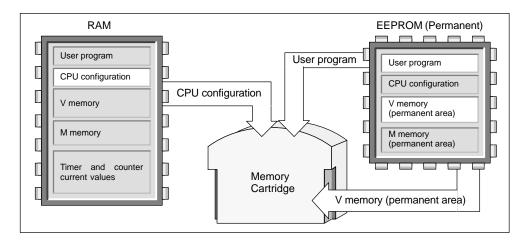

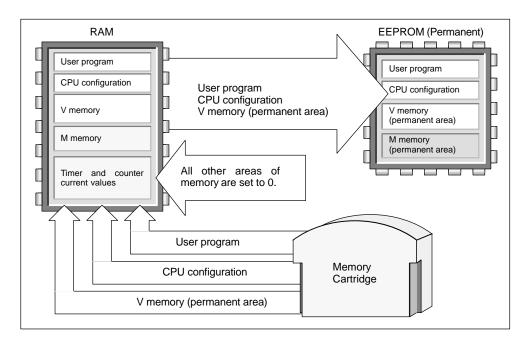

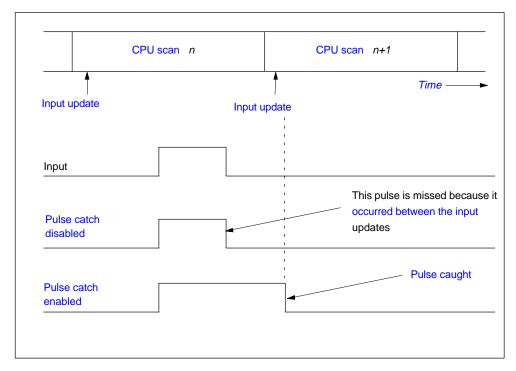

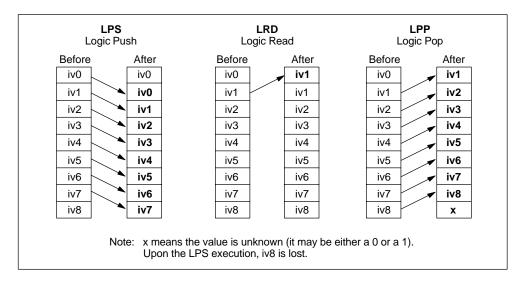

| PPI Local Connection            |                    |